您好!

我们喜欢使用 PLL LMX2572。 我们使用 LMX2572EVM 和定制驱动程序。

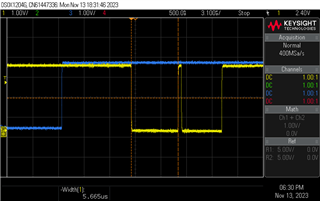

我们根据 LD_TYPE 模式(R59)观察到多路复用引脚的不同行为。 在模式0 (VCO)下、我们观察到预期的行为。 然而、在模式1 (VCO+VTUNE)下、我们观察到 MUXOUT 引脚的可调查行为。

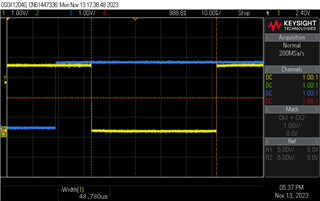

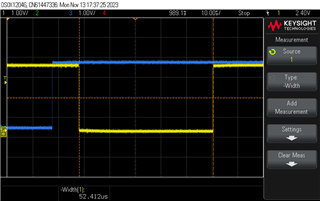

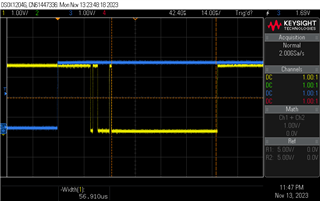

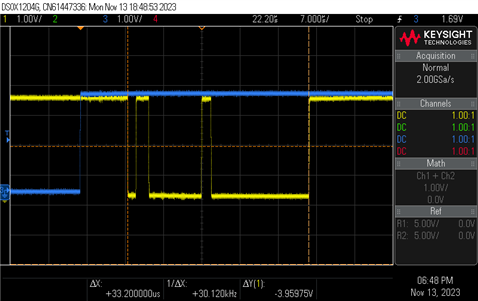

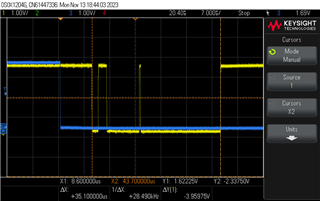

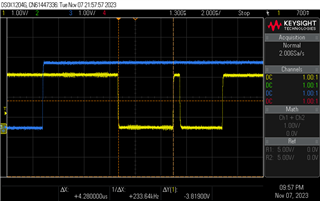

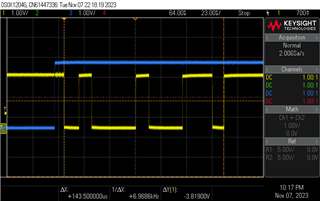

MUXOUT 引脚为黄色信号。

OSCIN = FPD = 100MHz、RFOutA = 3.3GHz、完全辅助模式、LD_TYPE = 1

OSCIN = FPD = 10MHz、RFOutA = 3.3GHz、完全辅助模式、LD_TYPE = 1

在模式部分辅助中,我们观察到相同的可调查行为(仅当 LD_TYPE=1时)。

这种行为是否正常?

我们还有一个附加问题、在 LMX2572数据表中、用于块编程的 R0 Add_Hold 字段在第7.5.4 p 22节中没有详细说明、我们是否需要对它进行块编程设置? 即使我们将其保持为0、它似乎仍然起作用。

提前感谢您的回答。

此致、

马洛