主题中讨论的其他器件: LMX2592

您好!

我们在新的 LNB 中使用 LMX2594。 它使用双转换架构将 Ka 频带信号下变频为 L 频带信号。 合成器在设计中用作 LO。 我已将我们的设计的方框图附加到该电子邮件中。 我们的合成器的一些关键参数包括:

- 50MHz 单端基准

- 200MHz FPD

- VCO_A = VCO 内核、VCO_B =通道分频器(2)

我们面临的问题是我们的合成器产生了有害的寄生信号水平。 这些杂散信号在 PLL 通电时产生、即使没有射频输入信号也是如此。 它们不是混合产品、因为它们不依赖于输入信号、也不会随输入信号功率或频率而调节。 不过、当基准频率发生变化时、它们确实会发生频率偏移。 我在下面附上了杂散图像(这些杂散在方框图中的 LNB 电路板笔记的输出处测量)。 对于我们当前的应用而言、这些电平太高、因为此时我们要求输出电平约为-120dBm、以便我们的系统能够符合要求。

蓝色迹线是在进行任何修改之前我们 LNB 的输出。 紫色迹线是被修改后的 LNB 的输出、在此我们设法降低了杂散水平。 执行此操作的人:

- 增加电源线上的滤波

- 将铁氧体磁珠(L202)替换为馈通滤波器(TDK MPN YFF15SC1C473MT000N)

这些看起来与我们200 MHz 的 FPD 频率相关、因为它们以200 MHz 为间隔。 此外、当我们更改 PLL 的 FPD 频率、例如100 MHz 时、杂散将分离100 MHz。 这向我表明它们是在 PLL 本身内部生成的。 我还在这封我们所测试的 LMX2594评估板的电子邮件中附上了屏幕截图、其中显示了这些频率下的杂散输出、这进一步向我表明这些是在 PLL 中生成的。

我们在其他产品中使用过 LMX2592、但没有遇到这些问题? 这可能是 LMX2594的固有问题。 TI 是否对此问题有任何了解? 是否有其他客户报告过类似问题?

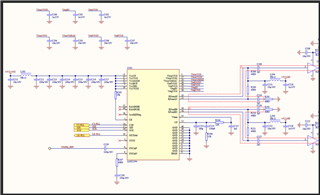

我已将合成器原理图的屏幕截图如下所示:

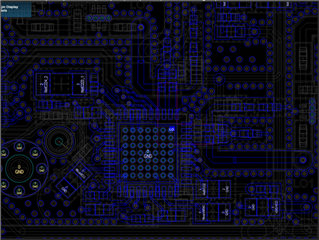

此外、我还附上了一些屏幕截图、其中简要描述了 PLL 所在的信号层。 请注意、每个层由一个 GND 平面隔开、以在各层之间提供隔离。

顶层:左侧的穿孔是50MHz 参考输入。 IC 位于底层。 VCC 偏置电容器在这层、连接到底层的引脚。

第3层:数字线路、SPI 和 LCK

L6:电源层。 芯片周围的跟踪是用于为 PLL 供电的+3V3。 底部和右侧显示的较大轨道是为整个板供电的5V5轨道。 电荷泵轨道是较小的轨道、位于 LMX2594的左侧和基准馈通的右侧。

L8:底层。 合成器、输出、环路滤波器、一些偏置电容器。

如果您注意到此布局中的任何有可能导致更高寄生输出的内容、请告知我们。

除了这些问题外、我们还想确定我们在原理图中所做的一些工作是否可以改进。 例如、对于 OSCin 电路和 LO 输出电路、是否应使用适当的平衡-非平衡变压器(例如电路中的平衡-非平衡变压器)来代替我们所做的电阻近似值(根据数据表)? 如果是、我假设差分阻抗为100Ohm、您能建议是否出现这种情况吗?