Other Parts Discussed in Thread: LMK61E2

您好

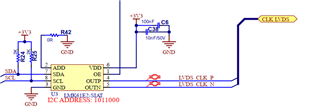

我正在使用 LVDS 时钟 lmk61e2-siat

LVDS clk (circuit1)信号通过柔性电缆发送到电路2 (电路2具有100欧姆电阻器)。

在连接柔性和第二个电路之前、我进行了阻抗检查、以确保没有短路。

CLK-P 与 GND 之间的电阻读取为45K 欧姆

clk-N 和 GND 之间的电阻读取值为50欧姆 (我预计、该值不正确、并且/或者 clk 可能工作不正常)

您是否知道从输出 CLK-P 和 CLK-N 到 GND 的阻抗 应是可接受的?

此致