主题中讨论的其他器件:LMX2592、

您好!

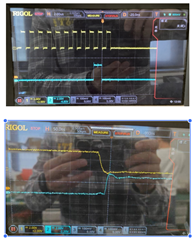

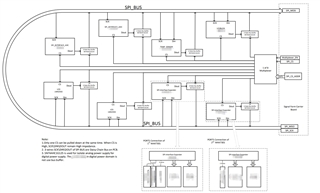

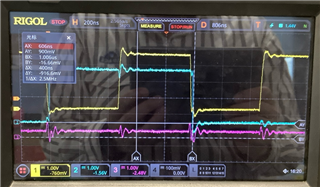

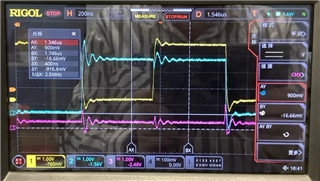

我们使用 SPI 总线来控制和配置系统中的器件、 连接到 SPI 总线的所有器件都是菊花链拓扑。 SPI 总线上有两个 LMX2592芯片、一个 LMX2572LP 芯片和其他5个器件。 但配置后、仅 LMX2592和 LMX2572LP 未成功配置、其他5个设备可正确配置。 MUXOUT 引脚上 LMX-DEVICE 的读回数据全部为0xFFFF。 在这种情况下,配置失败是不可避免的,曲线的 SCK 和 MOSI 喜欢这样. 我认为 SCK 和 MOSI 的时间序列是完美的,上升沿和下降沿的电压振铃是输入的阈值。