请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

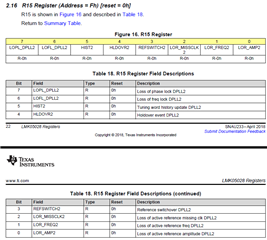

器件型号:LMK05028 我正在尝试获取 PLL 锁定状态。 我发现这三个寄存器具有一些位来指示是否失锁。 这些是获取状态的正确寄存器还是一些其他寄存器? 数据表对寄存器描述不多。

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

我正在尝试获取 PLL 锁定状态。 我发现这三个寄存器具有一些位来指示是否失锁。 这些是获取状态的正确寄存器还是一些其他寄存器? 数据表对寄存器描述不多。

尊敬的 Dhruv:

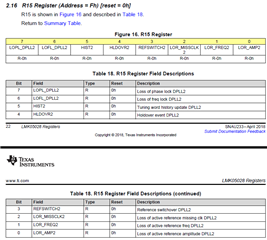

很抱歉耽误你的时间。 以下是有关建议使用的状态位的更多详细信息:

这些位表示实时状态并且会自行清除。 其相应的中断(附有_INTR)是一个粘滞位、表示您必须清除该位。

这有什么用吗?

此致、

珍妮弗