您好!

对于时钟缓冲器 CDCDB800、我们可以通过启用 SMB 使能位(OUT_EN_CLK)或通过 OE#硬件引脚启用 clk 输出。

a)如果 我打算使用 SM 总线寄存器而不是硬件引脚、那么该寄存器设置在 断电后是否会保持不变?

b)我们是否需要 OE#引脚和 OUT_EN_CLK 来启用时钟输出?

C)在其数据表中规定、OE#引脚必须连接到微控制器 GPIO 引脚才能设置为高电平或低电平。 我们可以使用上拉或下拉电阻器而不是微控制器吗?

谢谢。此致、

Shekha Shoukath

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好!

对于时钟缓冲器 CDCDB800、我们可以通过启用 SMB 使能位(OUT_EN_CLK)或通过 OE#硬件引脚启用 clk 输出。

a)如果 我打算使用 SM 总线寄存器而不是硬件引脚、那么该寄存器设置在 断电后是否会保持不变?

b)我们是否需要 OE#引脚和 OUT_EN_CLK 来启用时钟输出?

C)在其数据表中规定、OE#引脚必须连接到微控制器 GPIO 引脚才能设置为高电平或低电平。 我们可以使用上拉或下拉电阻器而不是微控制器吗?

谢谢。此致、

Shekha Shoukath

Shekha,

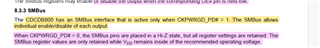

a) 否、断电后寄存器值将丢失 。 从 数据表可以看出、 "SMBus 寄存器值仅被保留、而 VDD 保持在建议的工作电压范围内。"

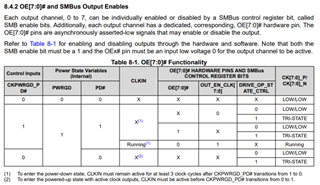

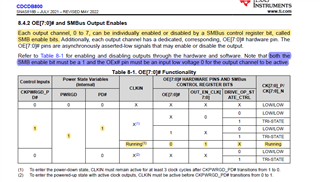

b) 是的、您需要 同时设置 OE#引脚和 OUT_EN_CLK 可启用时钟输出 。 "请注意、要使输出通道有效、SMB 使能位必须为1、而 OEx#引脚必须为输入低电压0。"

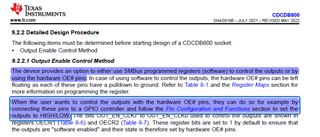

C)数据表提到 OE#引脚通常连接到 GPIO。 但是 是 如果要将 OE#设置为常量值, 您可以使用 上拉或下拉电阻器 来修复高电平或低电平状态。

此致、

将会

您好!

感谢您的回复。

请您澄清以下疑问吗?

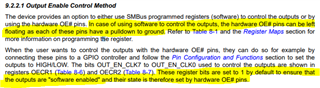

1. 在下图中,规定"SMBus 寄存器值仅保留,而 VDD 保持在建议的工作电压范围内"(以粉色阴影突出显示) 。 当 PWRGD_PD =0时、会发生这种情况。

由于此插卡将被插入服务器主板的 PCIe 插槽中、如果我们关闭电源、整个主板组件的电源将被切断、这意味着 VDD 到时钟缓冲器的电源也将被切断。 那么、由于它没有非易失性存储器、它如何保留寄存器设置?

2.

上图中指定了启用 CLK 输出(以蓝色突出显示)所需的 SM 总线使能位和 OE#引脚。

在下图中、假设需要 OE#或 SM 总线使能位(以蓝色突出显示)、哪种方法是正确的?

此致、

Shekha Shoukath

石家

1) 1)如果是对输出使能进行 SMBus 控制、 如果所需状态与默认状态(已启用)不同、则需要发送 SMBus 命令、以便在断电时将 OUT_EN_CLK#寄存器设置为所需状态 。 但是、如果您使用 OE#引脚设置输出使能、那么您无需担心断电时发生的任何设置更改。

2)两者都是正确的,但它是令人困惑的。 表8-1显示了输出使能功能的内部逻辑。 第9.2.2.1节描述了在给 OE#引脚和 OUT_EN_CLK#位默认状态下的高级功能。 由于 OE#引脚和 OUT_EN_CLK#位默认都设置为启用输出、这意味着只要修改 OE#引脚 或 OUT_EN_CLK#位、就会控制输出使能功能。 很抱歉 、如果我之前的答案令人困惑、因为我参考了内部逻辑表。

此致、

将会