Other Parts Discussed in Thread: CDCDB800

您好!

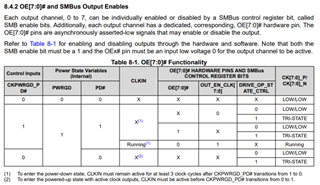

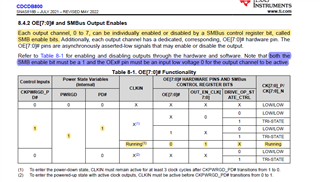

对于时钟缓冲器 CDCDB800、我们可以通过启用 SMB 使能位(OUT_EN_CLK)或通过 OE#硬件引脚启用 clk 输出。

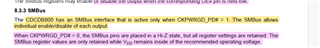

a)如果 我打算使用 SM 总线寄存器而不是硬件引脚、那么该寄存器设置在 断电后是否会保持不变?

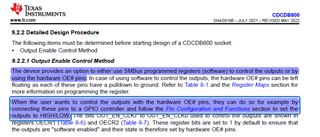

b)我们是否需要 OE#引脚和 OUT_EN_CLK 来启用时钟输出?

C)在其数据表中规定、OE#引脚必须连接到微控制器 GPIO 引脚才能设置为高电平或低电平。 我们可以使用上拉或下拉电阻器而不是微控制器吗?

谢谢。此致、

Shekha Shoukath