您好!

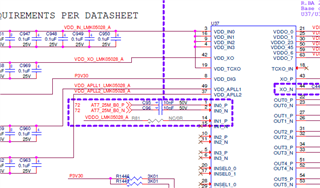

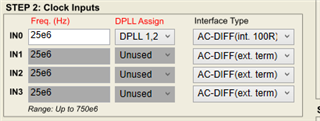

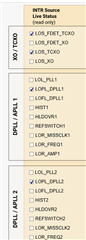

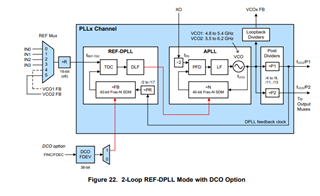

我有一个使用 LMK05028的设计。 我正在尝试在2个环路中使用它;REF、APLL 模式。

我在25MHz 的 IN0上有一个 LVDS 输入、在48MHz 上有一个 XO。 我将使用 PLL1和2分别输出100MHz 和312.5MHz。

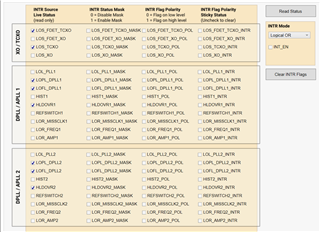

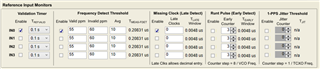

当我启用频率检测阈值时、无论有效 PPM 设置如何、PLL 都会卡在保持模式。

如果我在验证状态期间禁用频率检测、PLL 会报告频率已锁定、但从未显示为锁相。

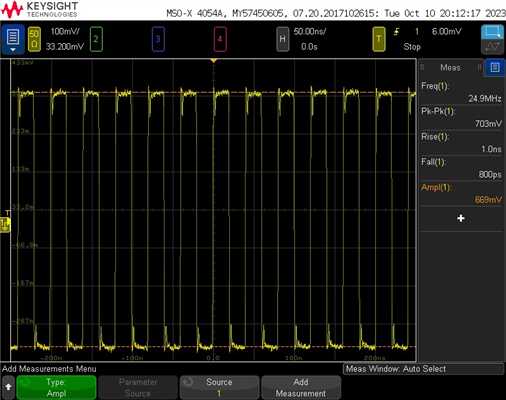

当我探测输入和输出时、我可以看到相位之间没有相关性。

附件为 TCS 文件。 请告诉我是在设置中缺失了什么内容、还是可以通过某种方法调试设置。

谢谢。

本·希尔特