主题中讨论的其他器件: LMX2820、 LMK61E2

团队、

我们运行时钟设计工具并获得以下解决方案。

10MHz 时钟输入、VCO 以3.2G 运行、然后生成160M、40M、25M、10M 输出。 方框图未在引脚43和44 OSCIN/OSCIN*上显示外部 VCXO。

我们是否仍需要在那里连接 VCXO。

非常感谢!

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

它取决于 所需的相位噪声、输入基准的相位噪声以及输入基准频率选项。 对于在20MHz 相位检测器处运行 PLL2的10MHz OCXO、由于锁定 PLL 所需的大 N 分频比、输出噪声完全由输入基准噪声决定。 如果您可以在160MHz 载波上接受从12kHz 到20MHz 的250fs RMS 抖动、并且您的10MHz 基准具有 OCXO 或更高质量、则 不需要 VCXO -您只需有效地调节输入基准噪声即可。 借助良好的 VCXO、在相同的集成带宽和相同的输出频率下、抖动性能更像是100fs RMS。 您还可以将输入基准更改为100MHz 或320MHz 等更高的频率、在仍然实现100fs RMS 抖动性能的同时无需使用 VCXO。

需要的性能是什么? 这可能表示在某个频率下的集成抖动和某些载波偏移集成带宽上的集成抖动;也可能表示在给定载波频率的特定偏移下的相位噪声。 如果需要比10MHz 输入振荡器的预期性能更好的性能、可以增加输入振荡器频率吗? 这些问题的答案决定了是否需要 VCXO。

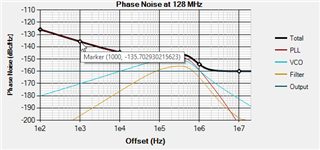

在1kHz 偏移时、限制因素实际上是 PLL 1/f 噪声-即使使用"完美"的输入振荡器、LMK04832也无法满足请求的要求。 假设载波为1GHz、偏移测量为10kHz、LMK04832 PLL2 1/f 噪声的特性为-128dBc/Hz。 重构为128MHz 载波、20 * log ( 128MHz / 1GHz)=-17.8dBc/Hz 调整、或在128MHz 载波、10kHz 偏移时-145.8dBc/Hz。 由于1/f 噪声 降低10dB/十倍频程、因此如果将偏移降低十倍频、噪声将增加10dB;在1kHz 偏移时、我们计算出-135.8dBc/Hz、与 PLL 相位检测器频率或 VCO 频率无关。 仿真结果大致相符:

如果在128MHz 载波的1kHz 偏移下确实需要-140dBc/Hz、则需要一个 1/f 噪声至少比 LMK04832好4dB 的器件。 在整个 TI 产品系列中只有一个时钟器件可以满足该要求:LMX2820、其1/f 噪声比 LMK04832高约6dB。 请注意、LMX2820是一款高性能分数合成器、但 价格会相应上涨。

除了 PLL、假设我们有任何器件可以满足此要求:使用10MHz 基准、您可以将输出端的总基准噪声放大20 * log (128/10)= 22.1dBc/Hz; 因此、要在1kHz 偏移时满足-140dBc/Hz 目标、您需要 在1kHz 偏移时具有至少-162.1dBc/Hz 的基准、并假定具有理想的 PLL。 实际上、 1kHz 偏移处的相位噪声将是 PLL 1/f 噪声和基准噪声的总和、我们已经知道 LMX2820的最佳情况仅为-141.6dBc/Hz 左右; 因此、在总 ^ ^= 10 * log (10 μ V (1/f 噪声/ 10)+ 10 μ V (ref 噪声/ 10))的条件下、求解所需的基准噪声不超过-140dBc/Hz、频移范围为22.1dB、 我们得到 在偏移为1kHz 的基准上的要求大约为-167dBc/Hz。 这对于 OCXO 来说是不可能的、但对于 标准 XO 或抖动清除器来说、这是不可行的、而且可以在1kHz 偏移时实现这种相位噪声的 OCXO 将非常昂贵。 改用100MHz VCXO 会使1kHz 偏移要求提高20dB、但100MHz VCXO 上1kHz 偏移处的-147dBc/Hz 仍然只能在可调的 OCXO 上使用。 但是 、这距本底噪声足够远、因此 与同类10MHz OCXO 相比、其拉电流更容易、成本也更低。

如果真的很想在128MHz 载波上的1kHz 偏移时获得-140dBc/Hz、那么您的系统将看起来像这样:

如果这听上去不切实际、您要么需要放宽128MHz 载波的1kHz 偏移的-140dBc/Hz 要求、要么需要通过另一种方法来改善近端噪声 、例如、组合多个 PLL 来提高大于噪声功率的信号功率、 如 LMX2594双 PLL 板的第3.2节所示 (请注意、这不适用于同一 PLL 上的共享输出、因为它们的1/f 噪声功率是相关的-您需要完全独立的 PLL)。

感谢 Derek 的详细解释! 我将研究它、以在未来改进我们的设计。 根据应用手册 SNAA311A、我们构建时钟并希望其接近140dBc/Hz。 我还有来自 LMK61E2系列的时钟输入。 " TI 超低抖动参考源的一个示例是 LMK61E2系列晶体振荡器、其在1kHz 时也具有非常好的接近相位噪声–140dBc/Hz 介绍 www.ti.com 2用于医疗超声波系统的时钟 SNAA311A–2017年9月–2020年9月修订提交文档反馈 版权所有2020 Texas Instruments Incorporated 针对200MHz 载波的偏移"、所以我们认为可以达到140dBc。 。

我们将对其进行评估、看看。 当然、我们知道这是一个非常具有挑战性的规格。 系统中还有一个 Wenzel 时钟。

非常感谢!

晓辰

同样、关键问题是、如果您使用 PLL、您将从 PLL 获得1/f 噪声。 LMK61E2在200MHz 载波上的1kHz 偏移处确实可以满足-140dBc/Hz 的要求、但如果 LMK04832 PLL 1/f 在所需时钟频率的1kHz 偏移处高于-140dBc/Hz、则1/f 噪声将是主要贡献。

在应用手册中、评估的最终输出频率为80MHz、因为它最终是关键相位噪声时钟。

因此、在80MHz 下、1kHz 偏移时可达到-139dBc/Hz。 在128MHz 下,频率缩放会增加20 * log (128MHz / 80MHz)= 4.1dB。 如果在128MHz 载波的1kHz 偏移处要求-140dBc/Hz、那么您的 PLL 的1/f 噪声性能至少要高5dB。

顺便说一下:假设我们使用 Wenzel 501-04609A 10MHz OCXO、它在1kHz 偏移下声称为-165dBc/Hz、作为 LMX2820的输入(1/f 噪声性能至少优于5dB 的 PLL)。

与标准 Wenzel 501-27514型号进行比较、该型号在100MHz 载波上的1kHz 偏移下要求典型值为-150dBc/Hz:

希望这能为您提供足够的信息来正确校准您对 PLL 性能的直觉、并为您提供了前进的明确方向。 祝您好运、如果您有进一步的问题、我们很乐意提供帮助。