主题中讨论的其他器件: LMK5B33216

大家好、

请帮助审查该方法、如果我们错过了任何内容、请提供建议。

目标:我们使用单 PLL 模式、希望在不使用任何时钟分接的情况下将从系统与主系统同步。

方法:

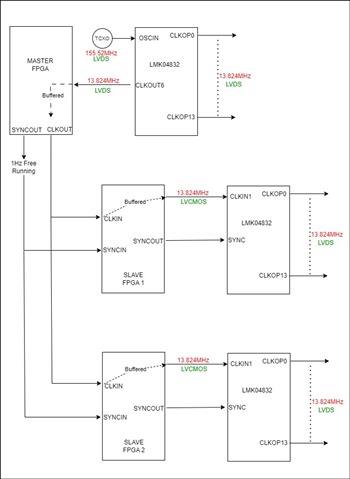

对于主器件、LMK04832将在外部 TCXO (155.52MHz)连接到 OSCin 引脚的情况下生成 O/P 时钟。 CLKOUT6的内部 FB 用于级联0延迟。

其中一个时钟输出(13.824MHz)反馈到主 FPGA。 该时钟和1Hz 同步脉冲从主 FPGA 传输(缓冲)到从 FPGA。

从 FPGA 接收时钟(13.824Mhz)、并将其用于连接到 CLKIN1引脚的 LMK 时钟输入。 从 FPGA 会将 SYNC 输出脉冲与馈送到 LMK SYNC 的 SYNCIN 同步、以便将 CLKOUT 与主系统同步。

一旦接通电源、从器件 LMK 就会与主系统同步。