主题中讨论的其他器件:LMX2594、、 USB2ANY

您好!

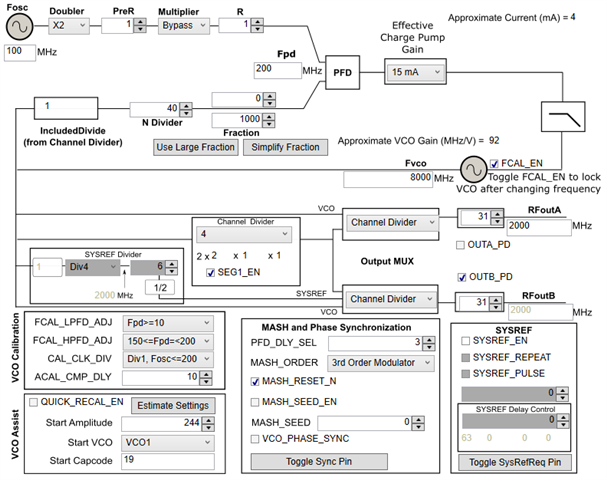

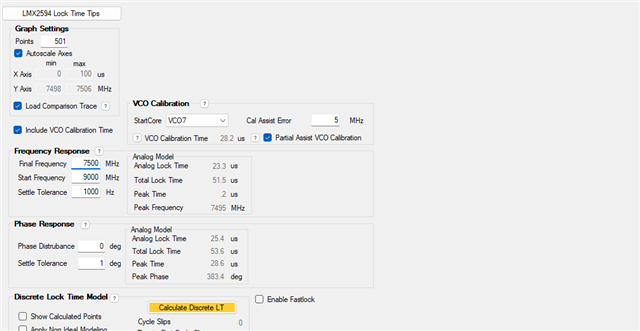

我当前正在对 LMX2594进行一些测量、并尝试找出"无辅助模式"和"部分辅助模式"的校准+锁定时间、以及"完全辅助模式"的锁定时间。

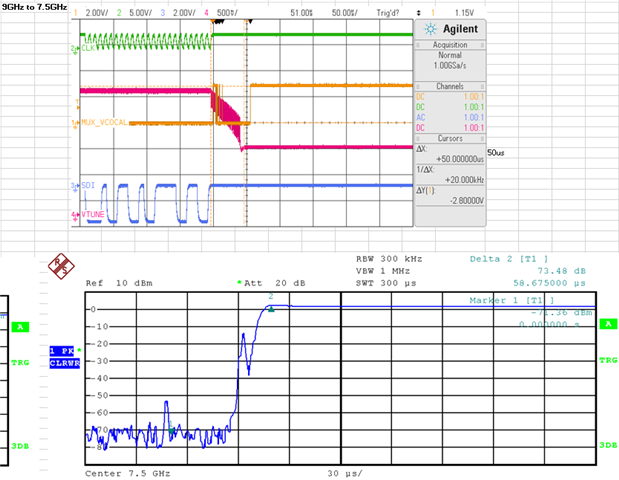

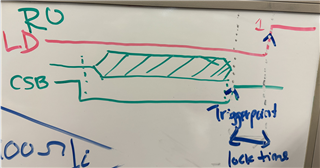

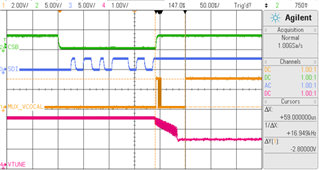

由于这里我们没有信号源分析器、因此我使用了示波器通过触发芯片的 CSB 来直接测量 Vtune。

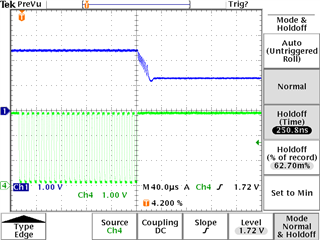

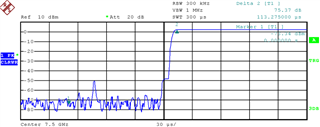

无辅助模式和 部分辅助模式测量的校准时间分别约为73us 和35-45us、请参阅以下内容(FCAL_EN=1时会触发测量):

与数据表中的50us 和35us (具有200MHz 振荡器)的语句相比、对于这两种模式、我的测量时间大约长10us 至20us、也许我的 ts 没问题、因为我在这里使用了100MHz 振荡器。

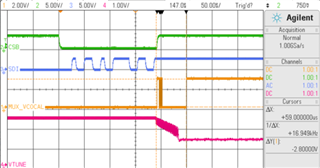

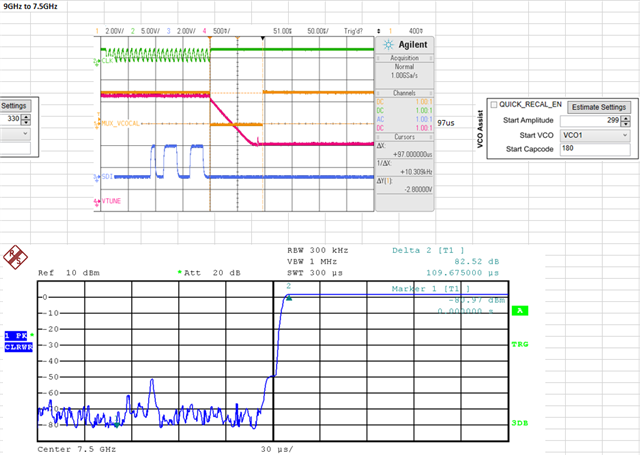

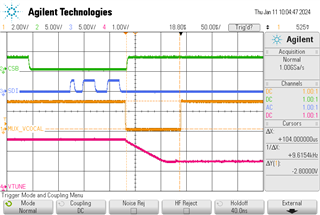

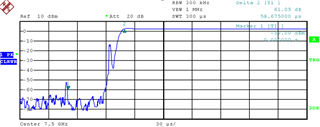

但对于完全辅助模式、锁定时间内 I 测量值为25us 至40us (跳过校准)、比5us 长得多:

为什么时间太长?

我的想法是、由于 Vtune 在 FCAL_EN=1被写入后从最大值或最小值改变(在实践中不像从一个锁定状态(freq.1)直接在很小的时间间隙中变为另一个锁定状态(freq.2))、可能需要更长时间是正常的。 但 TICS Pro 可以 只写入一个寄存器或所有寄存器、而不是只写入2或3个寄存器、以更改为所需频率...

在这个阶段、我想知道使用 Vtune 是否是测量校准+锁定时间的正确方法... 你对此有什么建议吗?

感谢大家取得进步、

XL

9GHz 到7.5GHz

9GHz 到7.5GHz

9GHz 到7.5GHz

9GHz 到7.5GHz  9GHz 到7.5GHz

9GHz 到7.5GHz