大家好、

客户有问题。

请您回答或评论吗?

- 关于数据表7.5.2、我们是否每次更改 N 分频器时都必须写入 R0寄存器、即使 R0寄存器中的 FACL_EN 设置为1?

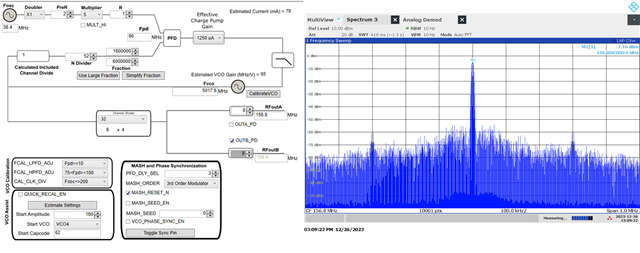

- 如何使用 VCO 校准? 我们是否必须单独为"部分关闭"、"关闭"和"完全关闭"选择"辅助/无辅助"?

- 当我使用 VCO Core1时、哪种类型的协助更好?

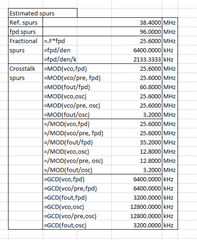

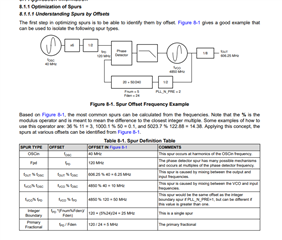

- 客户发现、N 分频器越大、杂散就越小。 N 分频器越大、噪声是否更好?

- MASH 顺序和杂散之间是否存在关系? (例如:较大的 MASH 顺序会导致较小的杂散)

- 关于数据表6.5 (5)"干净 OSCin 信号"、 PNPLL_ 1/f 是否包含 OSCin 的相位噪声?

- 关于数据表6.5 (5)、 PLL_Flat 公式中的 N 是多少?

- OSCin 压摆率越高、相位噪声越小。

参考信号的相位噪声与 PLL 输出的相位噪声之间是否存在关系?

此致、

转至

+

+