Other Parts Discussed in Thread: CDCE6214-Q1, CDCE6214

主题中讨论的其他器件: CDCE6214

您好!

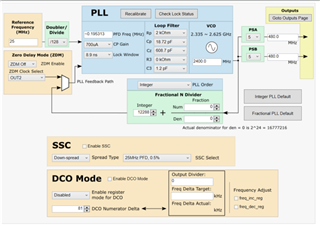

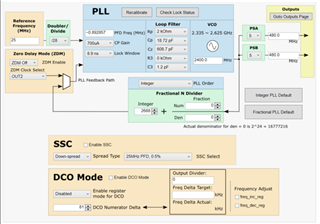

我有一个 CDCE6214-Q1开发套件、开箱即可使用、具有很好的标准设置。 但是、当我更改默认值1的默认倍频器/分频器(DD)设置并将分数 N 分频器(FND)设置的整数部分相乘时、会出现一些组合会意外地阻止 PLL 锁定。 我使用的所有设置都让 VCO 在2400MHz 上运行。 单击"重新校准"并检查所有更改的锁定状态。

我的应用中需要 DD = 100。 请告诉我如何实现。

从 DD = 1和 FND = 96的默认值开始、我已锁定 VCO = 2400MHz。 我可以将这两个变量增加到

DD = 27、FND = 2592、VCO = 2400。 (我尝试了 DD = 2、4、8、16、32、然后一直尝试到它起作用的地方)

但是

DD = 28、FND = 2688、VCO = 2400仅锁定部分时间、且

DD = 29、FND= 2784、VCO = 2400未锁定

从另一侧开始、我的锁定位置

DD = 200、FND = 19200、VCO = 2400

下至

DD = 129、FND = 12384、VCO = 2400

爬虫程序不再位于

DD = 128、FND = 12288、VCO = 2400

我尚未触摸系统中的任何其他设置。 是否有应更改的环路滤波器设置等?

谢谢。

Børge