Other Parts Discussed in Thread: CDCI6214, TDA4VM, SK-TDA4VM, CDCE6214

主题中讨论的其他器件: TDA4VM、 SK-TDA4VM、 CDCE6214

您好、TI

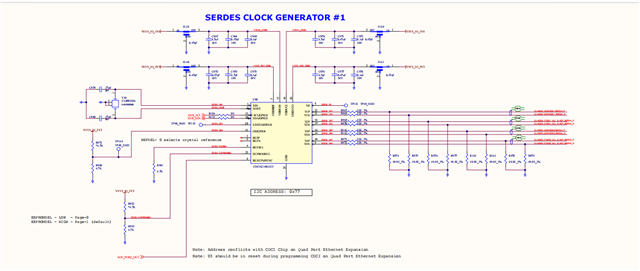

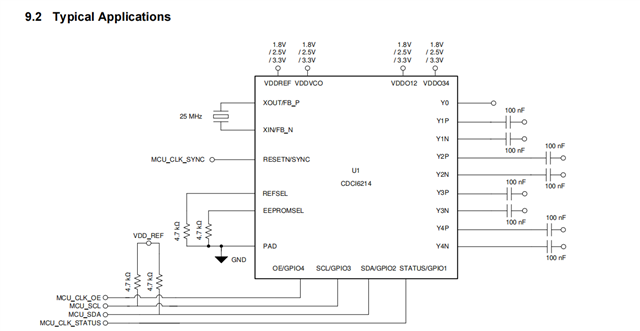

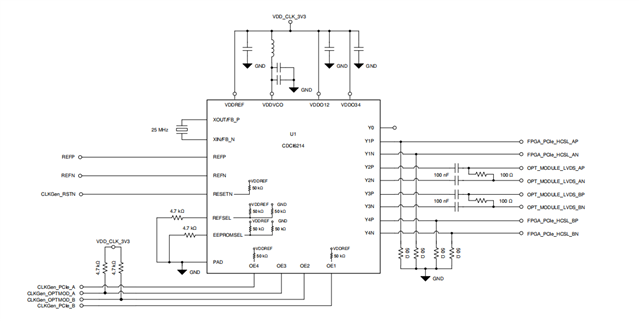

我们使用 CDCI6214作为 PCIe 时钟 支持。 现在、我们找不到它的 IIC 地址(0x77)、可以在 TDA4VM EVM 中获取 CDCI6214 (100Mhz)的时钟。 因此、我们想知道:

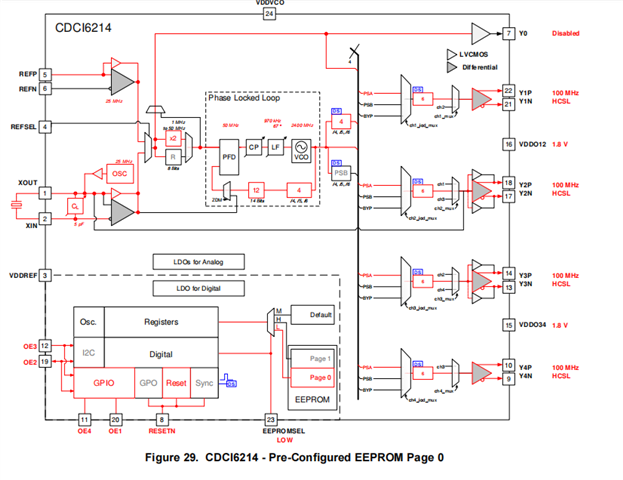

1 CDCI6214是否是驾驶员? 在 TDA4VM 的 SDK 中没有适用于该处理器的驱动程序、但运行正常。 它 可以在无驱动器模式下工作?

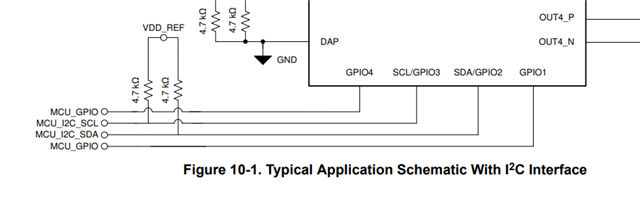

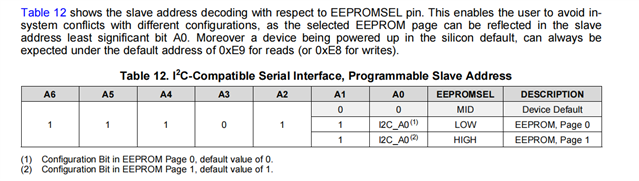

CDCI6214的2 EEPROMSEL PIN 在 SK-TDA4VM 中设置为低电平、但我们无法找到 I2C addr (0x77)。 我们尝试将 EEPROMSEL 上拉设置为3.3V、 可以获取 I2C 地址0x76。 是否与 CDCI6214手册冲突?

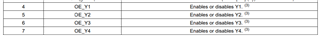

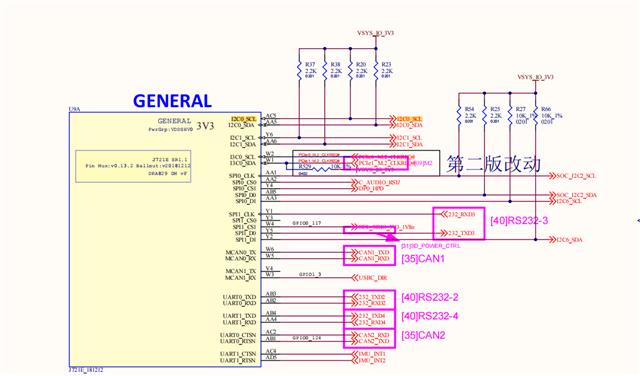

3在我们的定制 TDA4VM 电路板上、 我们 使用 page0将 CDCI6214的 EEPROMSEL PIN 设置为低电平、如下所示。 当 OE2和 OE3上拉至高电平时、所有输出时钟均正常;当 OE2和 OE3 挂起/下拉时、Y2P/N 和 Y3P/N 无输出。 为什么?

此致、

张