Other Parts Discussed in Thread: TLC555

您好!

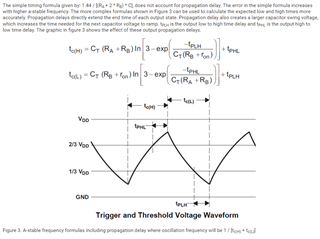

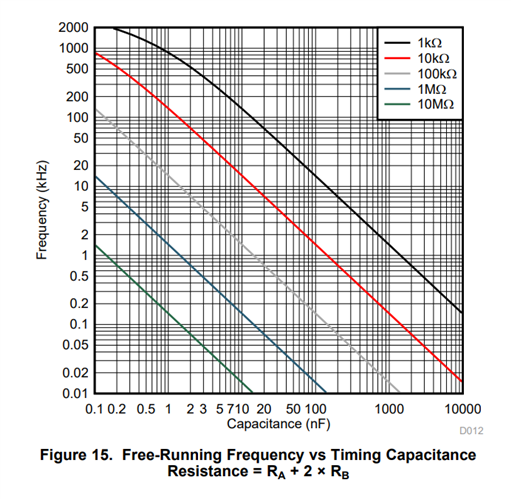

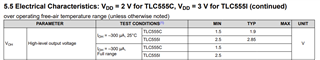

我想将 TLC555用作非稳态多谐振荡器、以生成占空比为50%的100KHz 方波。 我正在使用 TI 计算器、其中包含传播延迟、以估算输出频率容差。 我想通过选择容差为5%的 NPO/C0G 电容器来提高输出频率的容差、但我不知道如何使用 C0G 电容器计算改进的容差、因为该工具仅使用容差为10%的预定义电容器。 如果我要使用数据表中给出的公式、则不包括传播延迟。 您能否说明一下我如何计算/估算在 Vcc=5V 和3.3V 下运行、占空比为50%的100kHz 方波的输出频率容差。

此外、 当我未选择二极管选项时、该工具会抛出误差。 它显示"电阻值太小、请降低电容"、您能解释其原因吗?

对于这一要求,您是否有任何替代的经济高效的解决方案?