下午好!

我们在项目中使用了4个 LMX2594 PLL、我们面临着有关锁定时间的问题。

具体而言、我们有以下 PLL 输出频率规划 [以 MHz] 来保证:

| 3000 |

| 3200 |

| 3400 |

| 3440 |

| 3500 |

| 3800 |

| 3920 |

| 4420 |

| 4480 |

| 4600 |

| 4720 |

| 4740 |

| 4760 |

| 4780 |

| 4800 |

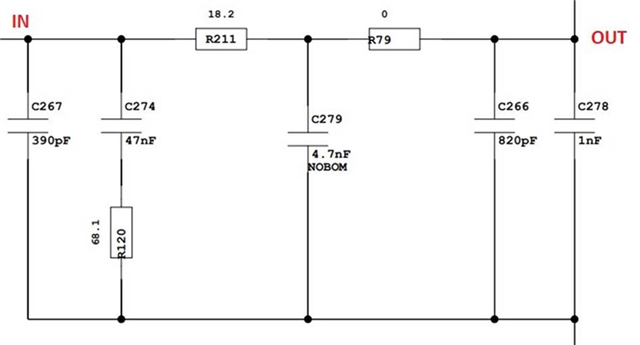

我们使用完全辅助模式和以下环路滤波器:

以下频率变化显示了200us 至400us 量级的锁定时间

- 起始频率:从4420 MHz 到4800 MHz ->停止频率:3920MHz

- 起始频率:4600 ->停止频率:3000 MHz、3400 MHz

- 起始频率:4480 MHz ->停止频率:3000 MHz、3200 MHz、3400 MHz

- 起始频率:4420 MHz ->停止频率:3000 MHz、3200 MHz、3400 MHz

- 起始频率:4600 MHz ->停止频率:3440 MHz

- 起始频率:4480 ->停止频率:4420 MHz、3440 MHz

即使使用 PLLatinum 工具的环路滤波器也不会缩短锁定时间。

我们将测量在最后一次 PLL SPI 写入后启用计数器的锁定时间、并在 MUXout 引脚(设置为锁定检测)转到逻辑1时将其冻结。

为了改善锁定时间、我们应该检查什么?

感谢您的支持