主题中讨论的其他器件:LMK04832

您好!

当我们使用较新版本的 TICSPRO (用1.7.6.2、1.7.7.1、1.7.7.2进行测试)上的将设置加载到 LMK04832评估板时、PLL2不会锁定。 我们必须手动将 N 分频器值设置为错误的值、然后设置正确的值以获得锁定。

我们有一台旧版本为1.7.0的 PC。 寄存器写入需要花费更多的时间、但最终当所有寄存器写入后、PLL2将正确锁定。

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好!

当我们使用较新版本的 TICSPRO (用1.7.6.2、1.7.7.1、1.7.7.2进行测试)上的将设置加载到 LMK04832评估板时、PLL2不会锁定。 我们必须手动将 N 分频器值设置为错误的值、然后设置正确的值以获得锁定。

我们有一台旧版本为1.7.0的 PC。 寄存器写入需要花费更多的时间、但最终当所有寄存器写入后、PLL2将正确锁定。

我有两种猜测可能会发生什么情况:

我已尝试在我的终端复制该问题、但我看不到它。 该问题可能与环路带宽有关、或者可能与您正在使用的 TCS/hex 文件相关。 如果您可以共享配置、我可以尝试使用该特定配置复制问题。

Derek 您好!

我的同事发现、.tcs 文件中存储了一个错误的寄存器值。

这是他的答案

已保存的.tcs 文件中有一个错误。 我已经更正了一个文件、两个 PLL 在文件加载后锁定。

它是第一个"Settings_LMK04832_SyncEN_Pll1Pll2 DLD_1SHOT_PLL1_R25_PLL2_DIV_DZM clkout8_SREF_PD_SYNC Nested_Reclockt_No 500MHz CLKout2_TCS_HO19_Test."

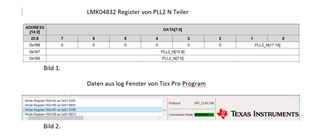

Tics Pro 加载的文件。 在图2上、在错误的数据字段处标记了一行、

09被写入 LMK04832寄存器0x167。 图1显示了用于实现主控振荡器

n 个 PLL2部件。 在左列中、我显示了以上.TCS 文件中的错误行。 这导致了

在 PLL2分频器 N 中写入了错误的数据、因此 PLL2没有锁定。

在本例中、N = 50应该是这样。

我已使用右侧列中的值更正了.tcs 文件、并在一个新文件中:"MK04832_SyncEN_Pll1Pll2_DLD_1SHOT_PLL1_R25_PLL2_DIV_SYNC_DZM_CLkout8_SREF_PD_SYNC_DISSYSREF_CLKout2_CLKOUT_R19_CHECK_CHECK_TSCM_CORP.19_TSCON_T." Nested_Reclockt_No 500MHz。

现在、加载正确的文件 PLL2后、它会立即锁定。

——错误 --正确

NAME122= R.389 NAME122= R.389

VALUE122= 91913 VALUE122= 91904

--in 十六进制 -以十六进制格式

VALUE122= 0 x 16709 VALUE122= 0x16700

我还将向您发送两个.TCS 文件。 一个是原始文件:"SETTINES_LMK04832_SyncEN_Pll1Pll2_DLD_1SHOT_PLL1_R25_PLL2_DIV_SYNC_DZM_clkout8_TCS_ Nested_Reclockt_No SREF_CLOUT2_PD_SYSREF_HO19_Test." 500MHz

该文件由 Tics 保存、并且我已手动更正另一个文件:"SETTING_LMK04832_SyncEN_Pll1Pll2_DLD_1SHOT_PLL1_R25_PLL2_div sync_DZM cl应为 SREF_PD_PRO_SYNC Nested_Reclockt_No、500MHz SYSRTO2_19_Corr_Test."

我认为这应该有助于在 Tics Pro 软件中进行故障排除。

加载这些.TCS 文件后、25MHz ClkIn0信号将显示三个已同步的25MHz、250MHz 和500MHz。 25 MHz 输出用作嵌套0延迟反馈信号。

此致、

亨德里克

e2e.ti.com/.../Settings_5F00_LMK04832_5F00_SyncEN_5F00_Pll1Pll2_5F00_DLD_5F00_1SHOT_5F00_PLL1_5F00_R25_5F00_PLL2_5F00_div_5F00_sync_5F00_DZM_5F00_clkout8_5F00_Nested_5F00_Reclockt_5F00_NoSYSREF_5F00_PD_5F00_SYNC_5F00_DISSYSREF_5F00_CLKout2_5F00_500MHz_5F00_HO19_5F00_Test.tcse2e.ti.com/.../Settings_5F00_LMK04832_5F00_SyncEN_5F00_Pll1Pll2_5F00_DLD_5F00_1SHOT_5F00_PLL1_5F00_R25_5F00_PLL2_5F00_div_5F00_sync_5F00_DZM_5F00_clkout8_5F00_Nested_5F00_Reclockt_5F00_NoSYSREF_5F00_PD_5F00_SYNC_5F00_DISSYSREF_5F00_CLKout2_5F00_500MHz