Other Parts Discussed in Thread: LMK04832

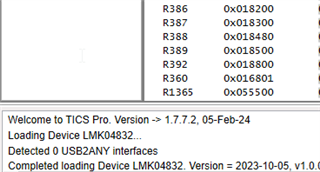

TICS Pro (v1.7.7.2)寄存器映射有不一致。 请参阅以下内容-最后几项

R387 0x018300

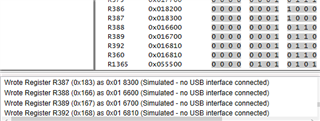

R388 0x016600 --左侧和右侧地址不匹配

R389 0x016700 --左侧和右侧地址不匹配

R392 0x016810 --左侧和右侧地址不匹配

R360 0x016810

R1365 0x055500

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

我新安装的 v1.7.7.2 LMK04832显示:

在 C:\ProgramData\Texas Instruments\TICS Pro\Configurations\Devices\Clock Generer-Jitter Cleaner (Dual Loop)\LMK04832\Texas Instruments LMK04832.inI (配置文件的主数据库)中、我在[Registers]部分中看到了:

NAME119=R386 MASK119=0 VALUE119=98816 NAME120=R387 MASK120=0 VALUE120=99072 NAME121=R388 MASK121=0 VALUE121=99456 NAME122=R389 MASK122=0 VALUE122=99584 NAME123=R392 MASK123=0 VALUE123=100352 NAME124=R360 MASK124=0 VALUE124=92172 NAME125=R1365 MASK125=0 VALUE125=349440

VALUE120、VALUE121和 VALUE122的值分别为0x18300、0x18480和0x18500。

我尝试加载 TCS 文件、发现 TICS Pro 在[MODES]部分接受的寄存器名称和地址值不匹配:

NAME120=R387 VALUE120=99072 NAME121=R388 VALUE121=91648 NAME122=R389 VALUE122=91904 NAME123=R392 VALUE123=92176 NAME124=R360 VALUE124=92176 NAME125=R1365 VALUE125=349440

为避免此数据损坏,名称密钥需要与 LMK04832.ini 中名称密钥的顺序和值相匹配,并且与每个名称密钥写入的值 需要属于该特定的名称密钥。 更正您的 TCS 文件[MODES]部分、以匹配 LMK04832.ini [Registers]部分的顺序。

出现此问题的根本原因是几个月前对 LMK04832配置文件中的寄存器顺序进行了重新排列、结合了迄今针对[MODGS]段密钥的未知顺序要求。 旧版 TCS 文件使用旧版订购方式保存了其[MODES]节键、现在加载不正确。

由于十年前做的决策不当(主要是选择允许重复的寄存器出现在寄存器映射中、请参阅 LMK04832中的 R0和 R0 (init)))、 我们无法通过解析[MODES]部分的值部分的地址并将其用作寄存器地址来有效地解决此问题。 但 如果您现在看到此问题、则意味着其他人也可能看到此问题、可能没有意识到为这三个寄存器写入了错误的寄存器数据。 幸运的是、在这个实例中、三个受影响的寄存器(R388、R389和 R392)是回读诊断寄存器、对配置不是至关重要的。 但 在其他配置文件中、这个问题也是一个潜在问题。 我将思考一个潜在的解决方案、并包含 TICS Pro 1.7.7.3的内容。

谢谢 Derek。 合并这些段太困难了。 因此我

1.删除了现有的"不良"TCS 设计

2.卸载 TICS Pro 1.7.7.3程序

3.删除程序/程序数据中的任何剩余文件夹

4.已重新安装 TICS Pro 1.7.7.3

从这里开始工作。 这样可以吗?

再次感谢。

从历史上看、让合成器/清理芯片正常工作(所有制造商提供的)始终存在一定的困难。 产品说明书并没有完全说明所有内容。 时钟编程工具也不会为您提供所需的一切。

作为用户、对 TICS Pro 的期望是

1.要按正确顺序编程的寄存器列表(重复次数很好!)

2。两次寄存器写入之间要等待的附加信息

a)可能有些偏置需要在芯片内部上电-因此等待几毫秒

b)可能有些东西需要在芯片内部锁定/校准-因此要么等待一段时间、要么回读一个寄存器

3、还有其他事情要知道吗?

如何获得第二部分?

此致、

约瑟夫

对于第1部分、我们规划了一个长期解决方案、将编程序列与寄存器映射数据分离;这样一来、您就可以独立于配置数据生成编程序列。 还有一些方法可以将配置数据表示为"我想要做的事情"的抽象、例如、我需要此频率计划、并且我需要同步相位、以便输入与输出对齐、 保存这些"用例"而不是仅保存寄存器映射数据有助于重构编程序列或其他生成的输出。 这是我 计划了很长一段时间的事情,它终于接近成果,但仍有几个月的时间。

对于写入之间的等待-生成编程序列的一部分也应 生成所有所需的等待。 此外、TICS Pro 需要能够在本机处理 I/O 管道中的这些等待。 再说一次、我已经 有很长时间了、有一个解决方案在工作、但需要更多的时间来实施。

对于此器件上的等待: 我建议从电源轨稳定时间开始等待10ms、直到 VCO 电容器稳定下来。 您可以 在所有电源轨电压都达到内部开启阈值几百 ns 之后向此器件写入、因此在电源发出电源正常指示时、您应该能够开始写入寄存器。 数据表还提到最后写入 PLL2 N 分频器的 LSB、因为这会触发 VCO 校准序列; µs OSCin 时钟的速度、校准序列可能需要不同的时间量、但100MHz PFD 频率大约为几百 μ s。 所以我想说从电源正常状态总共等待10ms、在此期间、您可以对器件进行编程、除了 PLL2_N 的 LSB;然后在这个10ms 后对 PLL2_N LSB 进行编程、并等待一个额外的500µs * 100MHz / F_OSCIN、或500µs、以最大值为准。 这些数字是一种沙状估计值、如果需要、可能会更快地启动、 但这需要一些特性来完全确定。

我还想指出的是、至少对于新器件、我一直要求进行特性评估、以便确定关键的 电源时序和 VCO 校准或器件同步等高级操作的设置/保持时间。 为了简化设计、我将继续在内部说明在数据表中捕获这些时序参数的重要性、尤其是因为 TICS Pro 寄存器 I/O 流水线本身就支持这些时序参数。