主题中讨论的其他器件: TLC555

迪亚尔斯、

目前、我们设计的电路首先将高电平信号(2.6V 或3.3V、最大驱动电流为20mA)输出到 LMC555CMX 芯片的第二个管脚、然后在几十毫秒甚至几十秒的间隔时间内为芯片供电。 请问这种用法是否会导致芯片内部的 CMOS 管产生闩锁效应、造成异常情况? 甚至损坏芯片?

谢谢

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

嗨、宁、

建议将我们几乎所有器件的输入电流限制为10 mA 或更低、这也限制了 ESD 二极管可以安全处理的电流量。 我们的计时器器件历史很长、我不知道与计时器相关的闩锁问题。 LMC555已有24年历史、我们的数据仅限于产品数据表。

如果它没有损坏,只是在引脚开始时出现高电平,然后恢复正常电源,将导致 LMC555芯片出现逻辑错误?

此场景需要在客户电路中进行测试以进行验证。 我们没有此器件的闩锁测试数据。 没有数据支持该问题的答案。

如果它可能永久损坏,是否意味着逻辑门芯片也必须考虑加电时序?

为了使逻辑电平有效、定时器必须至少为内部比较器提供最小电源才能正确偏置。 如果定时器的输入电平超出电源电压超过300mV、则可能会发生永久性损坏。 因此、在器件上电时应考虑上电电电电平和输入电平。

此致、

克里斯·费瑟斯通

嗨、宁、

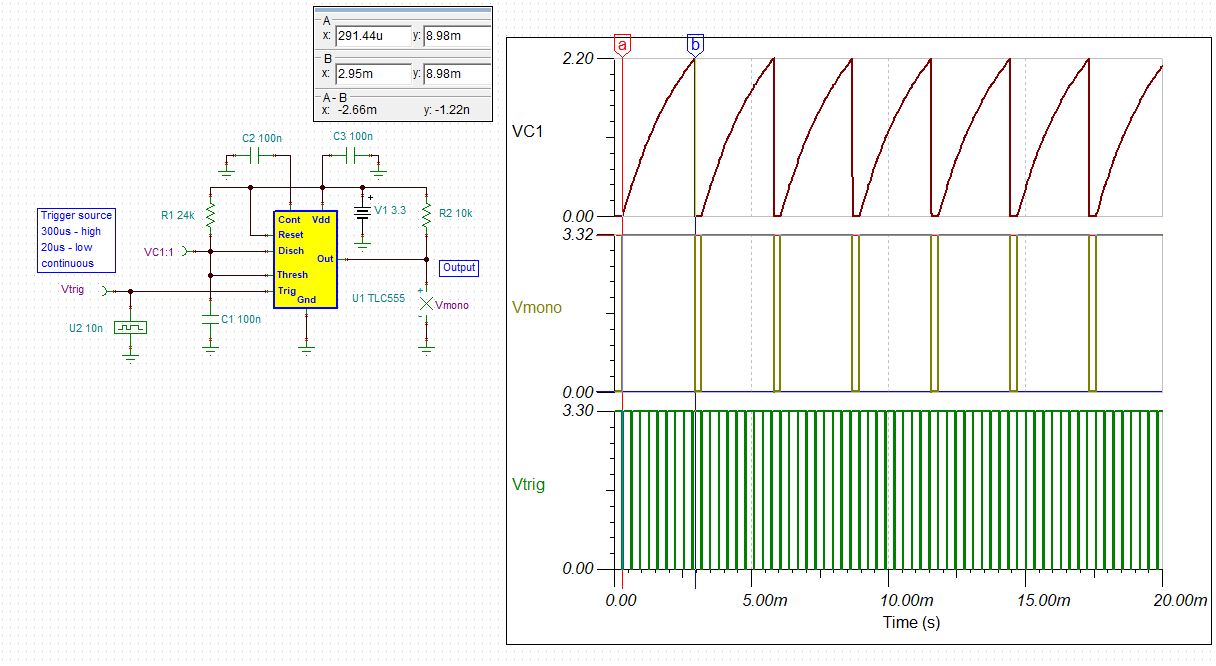

我们没有 LMC555的 SPICE 模型、因此我使用了 TLC555来检查电路的一般功能。 在下面您可以看到、原理图中显示的设计在触发引脚被拉至低电平时在输出上提供一个2.66 ms 脉冲。 我在这篇文章的底部包含了我的 Tina 仿真。

e2e.ti.com/.../TLC555-Mono.TSC

此致、

克里斯·费瑟斯通