有人可以请解锁以下主题:

我终于有时间解决它...

此致、

布拉德

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

有人可以请解锁以下主题:

我终于有时间解决它...

此致、

布拉德

您好、Brad、

我不确定如何解锁一个主题,与此同时,我想出来,我复制了 Derek 的回应如下:

"LMK04832 PLL1上的电荷泵最大为3.3V、因此如果需要使用电压范围顶部、可能会出现问题。 您可能需要使用有源运算放大器电路将电荷泵信号放大5/3.3倍、以访问全拉范围。

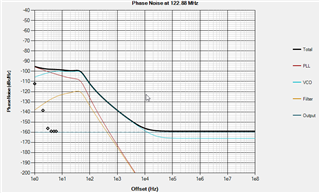

拉取范围(或者更准确地说、VCO 增益)肯定也会对环路稳定性产生影响。 例如、默认 PLL1环路滤波器设计为2.5kHz/V 增益斜率、从而产生以下40Hz 的41°相位裕度环路滤波器:

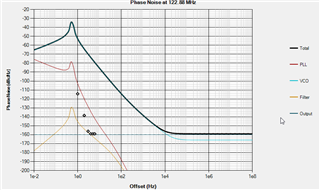

为了演示这个问题、我现在将增益降低1000倍、改为2.5Hz/V。 我不改变任何其他东西。 我的新环路带宽为0.5Hz、相位裕度为4.5°。

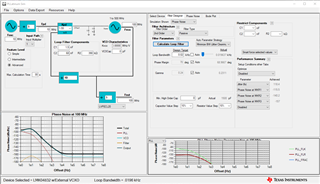

在设计环路滤波器时必须考虑 VCO 增益。 PLLatinum Sim 可以帮助解决此问题、 提供了一种 为振荡器设置 Kvco 增益特性的方法。

如果您在此期间有任何其他问题、请告诉我。

此致!

安德烈亚

不一定。 即使只能改变 ±4Hz、您仍然能够以比8Hz 环路带宽快得多的速度从+4Hz 跳到-4Hz。

VCXO 的调谐范围 设置 PLLatinum Sim 中的 Kvco、当环路带宽受 Kvco 影响时、它也会受到 KPD、FPD 和环路滤波器系数值的影响。 如果您具有足够高的 FPD 和 KPD 值、并且选择 不会显著 限制带宽的环路滤波器系数、则可以使用更高的带宽。 例如、我在 PLLatinum Sim 中测试了10MHz 基准和具有2Hz/V 调谐范围的100MHz VCXO、我可以看到、在最大增益和特定环路滤波器值下、我可以获得20Hz 环路带宽。

但是、您可能会 遇到 PLLatinum Sim 未建模的效果:VCXO 的调制带宽。 即使可以非常快速地更改调谐端口处的电压、但实际上、窄带 VCOCXO 无法如此快地响应调谐端口调制。 LMK04832EVM 上的 Crystek CVHD-950 VCXO 具有>10kHz 的调制带宽;在不同分销商上对一些 VCOCXO 进行采样,我看到1kHz 或更低的值很常见,有些则降至100Hz 或更低。 调制带宽的滚降将为系统增加另一个极 点、如果极点过于接近 PLL 和环路滤波器特性设置的其他极点、则会影响稳定性和环路带宽。 如果可能、请尝试使环路带宽至少比 VCXO 调制带宽小10倍。