Other Parts Discussed in Thread: LMX2571

我们在设计中使用 LMX2571为接收器降压转换器生成190 MHz LO。

当电路板温度达到大约65 °C 时、它会失锁。 似乎只是在窄温度范围内松了锁、我发现很难可靠地(按需)重复此问题。

我已确认输入时钟(100 MHz TCXO)和电源稳定。

您能提供有关测试/测量/验证什么以缩小原因的建议吗?

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好、Vicente:

是的、我可以监控 OSCIN、但也可以稍微间接地监控 OSCIN。 TCXO 的输出进入 LMX2571和 FPGA。 FPGA 对脉冲进行计数、并在距离 GNSS 的1pps 范围内将其锁存以测量时钟精度。 我们在100 MHz 上具有12Hz 的频率、因此我的假设是基准时钟是稳定的。 这不会拾取占空比或短期周期问题、但考虑到我的测量、不大可能出现这些问题。

我说"间接"是因为 TCXO 输出在这两条路径中分开、并且每条路径在源端都有自己的10欧姆电阻器、以便在数字域和射频域之间提供隔离。

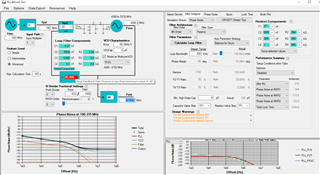

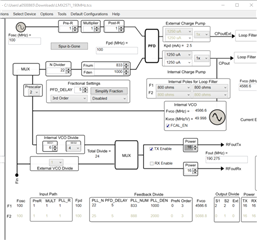

我的 N 分频器为45.655。 使用 PLLatinum Sim 时、它发出一条消息说 N 必须大于48、但我在任何文档中都找不到这一点。 符合 VCO 范围。 我缺少什么、这能解释我的问题吗?

您认为是否值得从 LX2571的输入引出 OSCIN (困难、但可行)? 还有事吗?

锁定不会自动恢复、但如果我重新初始化所有寄存器、它会恢复。 是否会锁闭失锁?

您好、Vicente:

我在我们测试它的所有装置上都看到了这个问题。 我们已经制造了几百个温度规格为55的区域、但是一个客户请求了65个、我们在前10个区域找到了这个值。

附件是我的.tcs 文件、其中包含它生成的寄存器。 我确认了在初始化后读回相同的值、当我发现问题时、这些值也仍然有效。 但有一个例外。 在 R0中、我有0x283。 我会在初始化期间设置 F1F2_MODE、但也会在频率应发生变化时设置。

此致、

彼得

您好、Vicente:

我看到 RFout 是190.275 MHz,我只是 想确定这是所需的频率吗? [/报价]可以。 当我最初提到190 MHz 时、为了简单起见、我进行了向下舍入。

您能不能在整个温度范围内监视 VTUNE 电压?应该是可能的。 这意味着有一根导线连接到处理室、这将增加电容、但希望这不会改变问题。

需要说明的是、您在谈论 CPout 引脚、25吗?

您能给我发送您的循环过滤器吗?三阶:270 pF 并联(5n6与560R 串联)。

您是否编程 R0以确保 VCO 校准?可以。 R0在 F1F2_MODE 和 FCAL_EN 置位时写入。

此致、

彼得

[/quote]

尊敬的 Pieter:

是。 当我最初提到190 MHz 时,为了简单起见,我进行了向下舍入。

我只是想确定一下。

请澄清:您在谈论 CPout 引脚,25?

-正确。

请监视 Vtune 过热。

您的目标环路带宽是多少?

使用您提供的配置和您提供的 C1/C2/R2值、我可以使用 PLLatinumSim 获得~132kHz 滤波器的环路 BW? 总的来说、您的环路滤波器看起来稳定、因此我认为环路滤波器不是解锁的原因。

请尝试 将分数引擎从三阶减少到二阶 、然后查看这是否可以解决解锁问题。 使用三阶时、您可能处于最小 N 分频器值的边界、而在高温下、这会导致解锁。

此致、

维森特

您好、Vicente:

我已经在设置中添加了第二个单元、并将两个阶上的 Σ-Δ 调制器阶数都更改为2阶数。 它没有区别。 我还将其更改为1、没有任何影响。

我可以通过查看降压转换器数据来间接看到合成器的输出。 我看到、新器件开始在较低温度(从大约50°C 开始)下出现杂散。 我要打开那个单元、看看能否通过一根导线来测量 Vtune。 我需要修改一些 metalwork 来做到这一点、因此可能需要一两天的时间才能获得结果。 如果您有任何其他东西可以认为我可以尝试缩小搜索区域、请告诉我。

此致、

彼得

除了我之前的回复之外、我现在还有一些其他数据(VCO 测量值)需要添加。

我已将我的测量结果以.pdf 文件的形式附上、其中说明了在.pdf 文件中是如何测量的。 所有测量都是使用新的二阶分数引擎完成的(尽管没有区别)。

我还尝试了其他方法:我将输出频率更改为200 MHz、以便 N 可以为48 (NUM=0;DEN=1000)。 这是为了看看它是否会产生差异。 我得到的结果与随附的.pdf 文件中显示的结果完全相同。

今天我还学习了一点更多的知识:

我还可以测量哪些其他东西来帮助我解决此问题吗?

尊敬的 Pieter:

浏览完 PDF 后、我有一个问题、您说要执行重置? 您能详细说明一下吗? 软件复位、重启吗? 您只讨论对板进行复位、因此我希望确保我了解复位的含义以及 什么 正在进行精确复位。

复位之后是否对所有器件寄存器进行重新编程? 我想问的是上一张幻灯片、您说您在哪里重新编程器件并重新校准 VCO。

如果您重置器件、则需要对其重新编程并重新校准 VCO。 重置为 LMX2571将导致器件恢复为器件默认状态、需要重新编程。 我相信,当你说"重新初始化"你是指重新编程?

您能否提供其 TCXO 的 DS? 输出摆幅/格式是什么? 如何将 TCXO 连接到接收器?

此致、

维森特

您好、Vicente:

再次感谢您的到来、非常感谢您的参与。

对不起,我的解释 不清楚。 我有两种类型的系统复位:

我对这两个器件都使用了"复位"、因为从合成器的角度来看、它们应该非常相似。 CE (引脚19)通过10k 电阻器被拉低。 它连接到默认为 tri 状态的 CPU GPIO。 复位后大约5秒、它只会变为 GPIO、然后被 CPU 拉高。 在这两种情况下、CE 线都将处于低电平、并在大约5秒后被拉至高电平。

该软件会等待100us、 初始化 LMX2571: 它向 R0写入 RESET 位、 数据表和 FCAL_EN 置位所需的默认值。 在复位条件下写入 R0后、没有延迟、就可以继续 从 R60一直向 R0写入所有寄存器。 最后一次写入 R0会设置 RECAL_EN 位。

"重新初始化"调用初始化函数、该函数先写入 R0、然后写入 R60至 R0、如上所述。

下面附上了 VCXO 的数据表。 VCXO 的输出连接到 OSCin (引脚34)、其中10R 串联。 还有另一个10R 并联、用于将 VCXO 输出连接到 FPGA。 \OSCin (针脚36)保持悬空。

感谢您发送编修。 这让我在启动时考虑了 VCXO 的稳定性、所以我明天会尝试将它添加到我的测量中。

尊敬的 Pieter:

好的、CE 由 MCU 上的 GPIO 引脚控制、默认为高电平。

因此、您可以开启器件电源并通过切换 R0[13]-> 1执行软件复位。

在这里、您的程序再次从 R60开始向下到 R0。

每次执行任何复位时、是否再次将 R60编程为 R0? 这是必需的。

好的、看起来它是 VCXO。 摆幅看起来不错。

您能否提供原理图的副本? 我希望了解它连接的确切程度。

此致、

维森特

您好、Vicente:

好了,CE 由 MCU 上的 GPIO 引脚控制,默认为高电平。

没有、它是通过10k 电阻器下拉为低电平 的、所以我会看到加电时的默认值。 在 GPIO 初始化过程中、CPU 会将其拉高。 这意味着它在上电大约5秒后被拉为高电平、而代码在拉为高电平后开始写入寄存器100us。

从这里您的程序从 R60再次开始到 R0。 [/报价]是的。

每次执行任何重置时,是否再次将 R60编程为 R0? 这是必需的。是的。 上电或命令后调用的 R0()函数将始终写入 Synth_Init (通过将 R0[13]设置为1),然后写入 R60至 R0。

您能提供原理图的副本吗? 我希望查看其连接的确切程度。您是否有电子邮件(或其他方式)让我私下分享? 我无法在公开论坛上分享公司原理图。

我目前正忙于我的测试、以便监控 VCO 和时钟。 我在示波器上的水平分辨率是50us/div、因此我实际上只关注时钟的包络、这并没有显示任何问题。 但是、由于我在监控时钟、我未能重现此问题。 确切地说还为时尚早、但可能时钟上的探头加载具有足够的效果来掩盖问题。 在更详尽的测试之后、我会在一天结束时获得更多信息。

此致、

彼得

[/quote]

尊敬的 Pieter:

是的,您可以发送电子邮件至 v-floresprado@ti.com 。

如有可能、请发送 pdf、这将使阅读过程更加简单。

此致、

维森特

您好、Vicente:

再次感谢您在解决复杂问题中提供的帮助。 为了闭合环路、我已将您的第一个响应标记为正确响应、因为问题发生在 OSCIN 引脚上。

但对于其他人来说、这并不简单:我的 CMOS 振荡器输出被分成两部分、一条路径包含高次谐波(我在示波器上看不到)的反射、这似乎使 LMX2571校准过程相混淆(这不是 VCO 问题)。 我们添加了一个非常小的15 pF 电容器来滤除高频分量、这解决了我的问题。