请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:LMK04832 主题中讨论的其他器件:LMK04828、

您好!

我们有一个关于 LMK04832/LMK04828的问题、

在我们正在处理 的新项目之一中、LMK04832将用于向 Xilinx RFSoC 生成时钟。

-

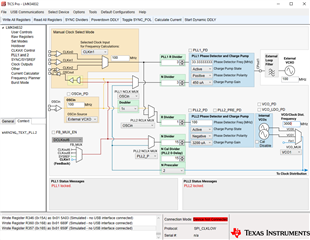

客户提到了输入外部时钟的选项、因此我们正在考虑将外部时钟输入馈送到 LMK04832的 CLKIN1

-

外部输入时钟为100MHz、具有-150dBc/Hz 的良好相位噪声

-

到 CLKIN0的板载参考时钟输入、CLKIN0也是一个100MHz OCXO 部件: KNBNTE100MFNFCAB

-

OSCIn 输入还将是100MHz VCXO

我们的疑问是、

-

可以将100MHz 的 PLL1参考时钟

-

PLL1的 PFD 有问题吗? 和 N 分频器、因此存在较大的

-

对于这种情况、您建议 PFD 的价值是多少? 因为 PLL1的 Fpd1是40MHz

请您对此事提出建议。

注意:在之前的应用中、我们将 CLKIN0的 TCXO 10MHz 用作 PLL1基准输入、PFD 为0.1/ 1MHz。

谢谢