主题中讨论的其他器件:LMX2595、、 LMK61PD0A2

你好, 我观察到一个令我困惑的现象。

当 LMX2520的基准信号设置为125MHz 时、不管输出频率是多少、都会有3.5GHz 的杂散输出(接近-70dBm)、这似乎是基准频率的高次谐波。 我没有找到有关 LMX2595参考频率杂散或 PFD 杂散的任何规格。 LMX2595的性能是否正常?

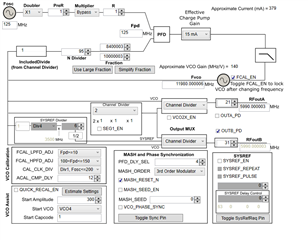

此外、当我使用 SMW200A 和 Reference Pro (LMK61PD0A2)提供的125MHz 基准测试 LMX2595EVM 时、我观察到了相同的现象。 这是我的 TICS Pro 设置、3.5GHz 杂散接近-75dBm。

当我将参考频率更改为130MHz 时、3.5GHz 伪波消失。 初步确定此杂散信号是由 OSCin 或 PFD 引起的。 能否消除或减少此杂散信号?