Other Parts Discussed in Thread: TLC555

主题中讨论的其他器件:TLC555

您好!

我想在单稳工作模式下使用 TLC555。 我有以下有关 IC 的问题

1.将输入触发为低电平或低于触发电平以生成单声道触发脉冲的最短时间是多少? 在数据表的哪里可以找到此信息?

2.一旦阈值引脚电压超过阈值电平,触发器将被重置,输出为低电平。 如果计时电容器通过放电 FET 完全放电之前存在触发脉冲、会发生什么情况?

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好!

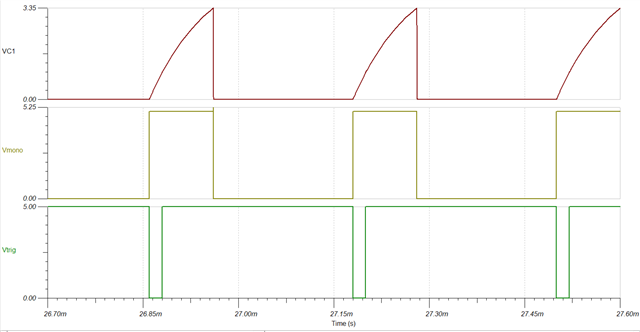

请参考我们的常见问题解答。 有一个表显示最短的触发时间。 我已经运行仿真来显示所述条件下的器件行为。 Vmono 是计时器的输出。 仿真附在这篇文章的底部。 请告诉我是否可以提供进一步的帮助。

e2e.ti.com/.../slfm003b-_2800_28_2900_.TSC

此致、

克里斯·费瑟斯通

您好 Manoj:

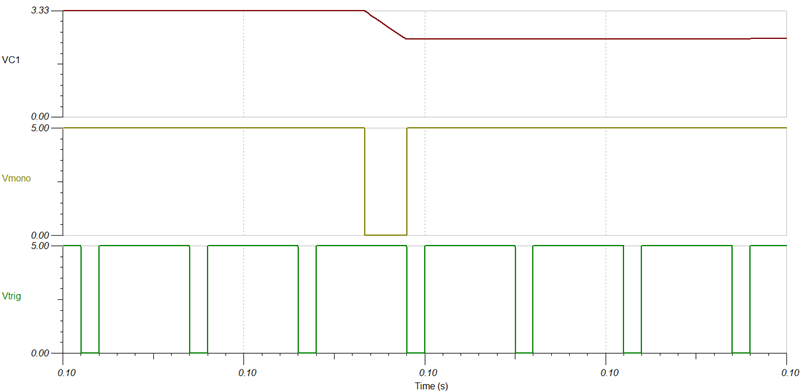

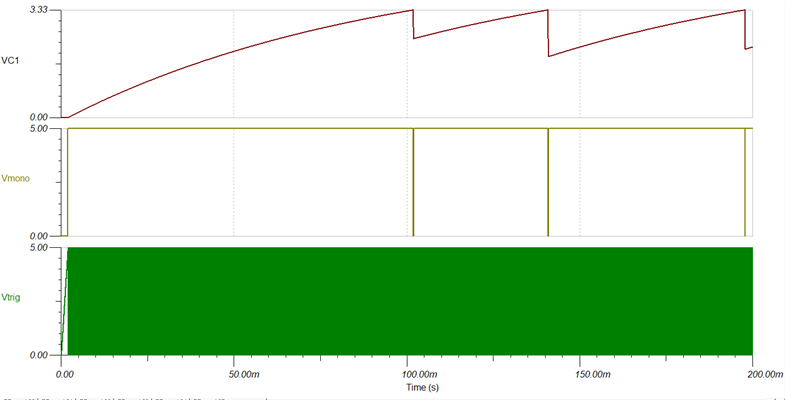

触发引脚优先、所以、无论触发脉冲状态是什么、输出都应该进行、即、如果触发变为低电平、输出应该变为高电平。 您可以在下面的仿真中看到这一点。 电容器不会完全放电、触发器会变为低电平、输出会变为高电平。 输出将保持高电平、直到电容器充电回至3.3V。

e2e.ti.com/.../slfm003b-_2800_28_2900_-_2800_2_2900_.TSC

此致、

克里斯·费瑟斯通