Other Parts Discussed in Thread: CDCE913, CDCE6214

主题中讨论的其他器件: CDCE6214

尊敬的 TI 支持团队:

我正在评估第 CDCE913以获得两个时钟、一个20MHz 和一个80MHz。 晶振为16MHz、PLL 频率为160MHz、输出频率值可以、使用 Y2和 Y3输出。

在应用中、需要知道两个时钟的相位关系、或将其设置为预定义值。

目前我无法获得这个值、相位看起来是随机的且不可控的、有时是好的、有时则不好。

我尝试做的事情:

- 配置所有寄存器以获得所需的频率

- 将 Pdiv2和 Pdiv3设置为零(RESET 和 STANDBY)

- 停止 PLL ( PWDN=1)

- 将 Pdiv2和 Pdiv3设置为2和8以获取正确的频率

- 启动 PLL ( PWDN = 0)

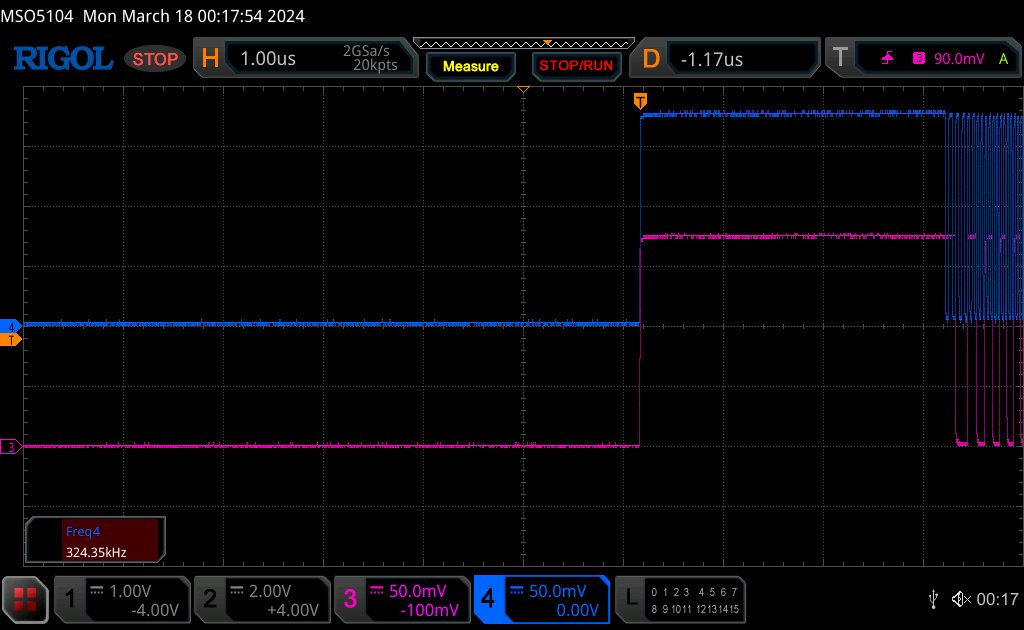

我发现、当 PLL 从随机值重新启动两个输出、并且不会像它们应该那样总是0 (此时、我假设必须从值0开始)、就像发生了某种干扰。

PLL 锁定时间过后、两个信号达到所需频率、但起始条件不可确定、因此相位也不可确定。

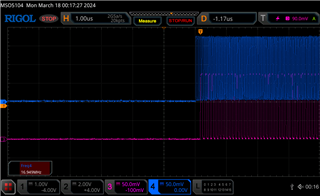

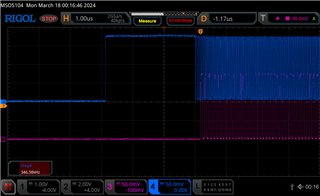

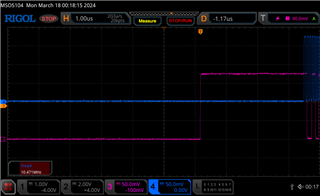

我有一些示波器捕获可供显示:

两个输出从0重新启动、从而进入

错误行为(不同的故障)

您能否建议如何获得稳定的启动条件?

此致、

安东尼奥