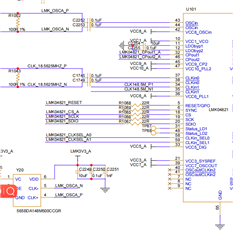

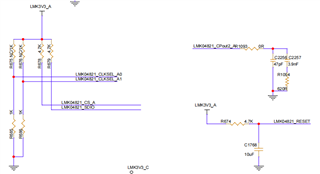

芯片 正常 以 3.3V 的电压供电。SPI 通信 失败。 FPGA 和 LMK04821之间只有电阻器、 不含 任何 其他 元件。

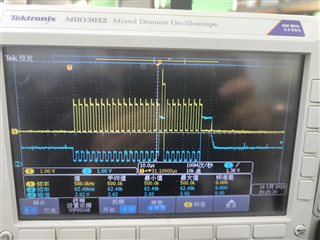

LMK04821 由 FPGA 控制、 CSn 不能 拉 高。 将 CSn 上的端接电阻更 改为 1K 并 将 到 LMK04821 的距离缩短为 1cm 并不 能解决 问题。 FPGA 和 LMK04821 共享 公共 接地。 测量结果 显示:

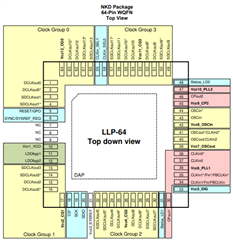

1. 系统在 没有 FPGA 负载的情况下上电时、 FPGA 的引脚状态 为 弱 上拉。 测量 电阻两端的电压时、 LMK04821 侧的电压 为 1.56V、 FPGA 侧的电压 为 2.10V 、因此 CSn 引脚的输入电流 为 540uA。

当 FPGA 加载 且 SPI 接口 保持 默认 状态 而不 发送 数据时、 将 CSn 引脚驱动 为 高 电平 会导致 LMK04821 侧的电压 为 1.62V 、 FPGA 侧的电压 为 3.30V、 CSn 引 脚的输入电流 为 1.68mA。

3、 在 第二个 测试 条件下、 通过 复位 管脚多次尝试复位 LMK04821芯片 、同时 监控 LMK04821 侧的 CSn 信号线。 但是、 没有任何 变化。 根据 关于 CSn 引脚 电流的数据表、 CSn 只能 作为 输入 接口、 最大 电流 为 ±5uA。 不过、 实际 测量值 与 数据表相差 数百 倍、 表明 CSn 处于异常功耗状态。

鉴于 LMK04821 只 需 稳定的 3.3V 电源 以及 RESET 引脚上持续的高电平或低电平 即可 正常 运行 、是否有可能出现上述错误状态、 解决 该 问题的最佳方法是什么?

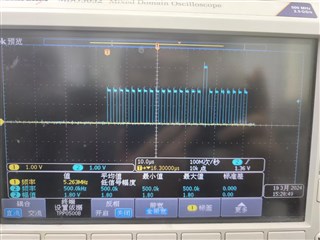

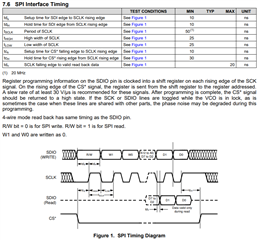

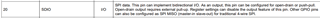

此外,在正常运行(端接 电阻22欧姆,SDIO 上拉电阻4.7K 到3.3V )时, SCK 高压仅为2V。SDIO 无法保持低电平。