主题中讨论的其他器件: LMK5B33216

您好、TI 团队:

我正在尝试为我们的一个设计评估 LMK05318B、具体要求如下:

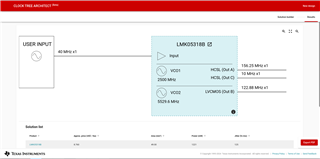

IN:40MHz XTAL、40MHz 恢复时钟

输出:156.25MHz (HCSL)、122.88MHz (LVCMOS)、40MHz (HCSL)和10MHz (LVCMOS)

使用单芯片 LMK05318B 是否可以实现此组合?

在 您的 webench 时钟树架构工具中进行测试、正如预期的那样、该芯片将生成 APLL1和2所需的两个任意频率。 此外、还给出了10MHz、如 VCO1所示。 对于40MHz、该工具建议使用另一个级联到其10MHz 输出的芯片。 那么、我的查询是:

- 当156.25MHz 不是来自的整数除法值时、芯片如何获得与156.25MHz 相邻的10MHz? (它仅是10MHz、不是任何其他频率可见)

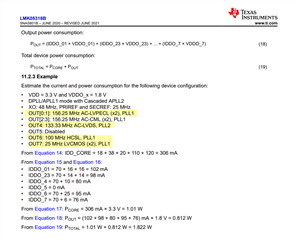

- 其中一个数据表 示例案例(第76页)显示了100MHz 和25MHz 的生成以及两个法国巴黎频率。 这些数字是通过什么配置得到的?