您好!

我设计了一个带有 LMX2572 8个 PLL 的电路板。

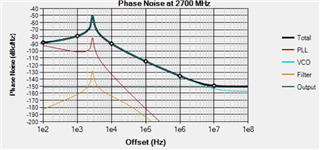

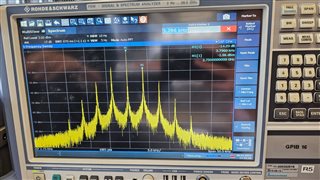

我将通过 SPI 对 PLL 进行编程、并获得目标频率、准确地说、我想将其用作载波频率、但这些会 在频率上显示一些噪声纹波(似乎是周期性的)或杂散、

正如我在 PCB 上检查的、它似乎约为3.7kHz。 来自 PLL 的 OUTB 被路由到 PCB 的边缘、再到 SMA 连接器。 PLL 使用精确的外部100MHz 频率发生器(10dBm)、这也解释了在目标频率下获得的良好结果。 我将在整数模式中运行 PLL 并且还将 SYNC 模式置于打开状态(这应该不会改变结果)。

目标频率2.75GHz:

目标频率2.8GHz:

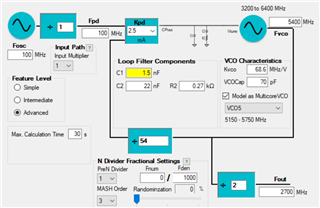

我的环路滤波器如下所示:

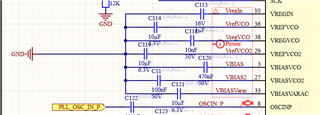

我已经按照数据表和评估板中的建议添加了所需的去耦

对于每个 PLL、我也有一个单独的 LDO:

我还尝试测量 VrefVCO 和 VBIAS 上的电压、但看不到任何噪声纹波。