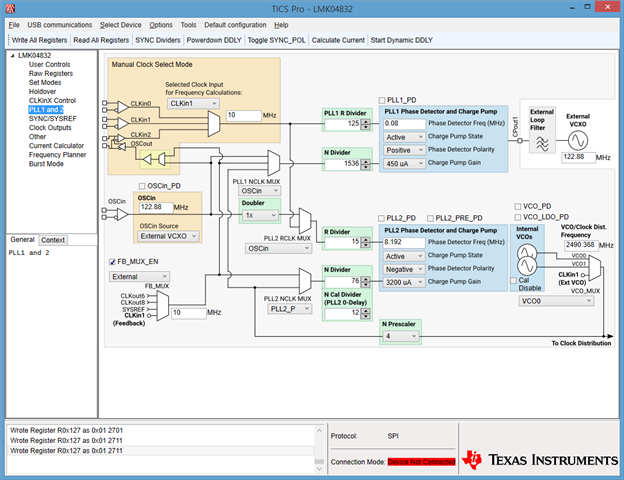

我使用的是双环路模式。

针对 PLL1的 CLKin1 (10MHz):使122.88MHz 生成

用于 PLL2的 OSCin (122.88MHz VCXO):使2490.368MHz 成为

当 Xilinx 的 Microblaze CPU 在初始引导期间设置 LMK04832时、PLL1和 PLL2都将锁定。

然而、当相同的值再次被写入 LMK04832时、PLL1或 PLL2 被解锁。

(特别是在设置地址0x138、0x147、0x161、0x168时)

提前感谢您的答复。

寄存器的配置值如下。

-------------------------------------------------------

| 0000 0090 0000 0010 0002 0000 0003 0006 0004 00D1 0005 0063 0006 0050 000c 0051 000d 0004 0100 0013 0101 000a 0102 0010 0103 0040 0104 0000 0105 0000 0106 0001 0107 0011 0108 0013 0109 000a 010a 0010 010b 0040 010c 0020 010d 0020 010e 0001 010f 0041 |

0110 0013 0111 000a 0112 0010 0113 0040 0114 0010 0115 0000 0116 0001 0117 0011 0118 0013 0119 000a 011A 0010 011b 0040 011C 0020 011D 0020 011E 0001 011F 0011 0120 0013 0121 000a 0122 0010 0123 0040 0124 0010 0125 0000 0126 0001 0127 0041 0128 0013 |

0129 000a 012A 0010 012b 0040 012c 0010 012d 0000 012E 0001 012F 0011 0130 0013 0131 000a 0132 0010 0133 0040 0134 0020 0135 0020 0136 0001 0137 0011 0138 0011 0139 0000 013A 0000 013B 0098 013C 0000 013D 0008 013E 0003 013F 0007 0140 0003 0141 0000 |

0142 0000 0143 0001 0144 00ff 0145 0000 0146 001A 0147 001A 0148 0002 0149 0042 014A 0033 014B 0006 014C 0000 014D 0000 014E 00C0 014F 007F 0150 0001 0151 0002 0152 0000 0153 0000 0154 007D 0155 0000 0156 007D 0157 0000 0158 0096 0159 0006 015A 0000 |

015B 00D4 015C 0020 015D 0000 015E 001E 015F 000b 0160 0000 0161 000f 0162 008C 0163 0000 0164 0000 0165 000c 0169 0058 016A 0020 016B 0000 016C 0000 016D 0000 016E 0013 0173 0010 0177 0000 0182 0000 0183 0000 0166 0000 0167 0000 0168 004C 0555 0000 |