主题中讨论的其他器件:CDCI6214、CDCE6214 、 LMK05318B

您好!

我想将 CDCI6214替换为 CDCE6214。

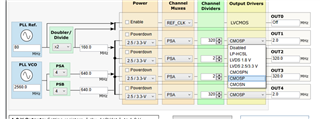

TICS Pro。 CDCI6214可以将 LVCMOS 输出设置为 CMOSP、CMOSN 和 CMOSPN。 然后、它还可以设置为 P+ N+、P+ N-、P- N+、P- N-。 这是什么意思? 我认为 P+ N+是极性。 我不了解 CMOSP、cmon 和 CMOPN 配置。

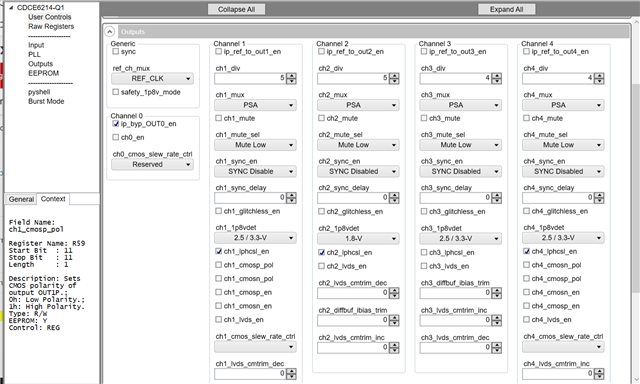

关于 CDCE6214、该软件只能将输出设置为 CMOSP、CMOSN、CMOSPN。 如何设置极性? 数据表显示了寄存器 R59[12]、R75[12]和 R59[11]、R75[11]控制着极性。 如何在软件中执行此操作? 如果 CMOSP/N 是极性、那么 CDCI6214配置中的 P+ N+是什么呢?

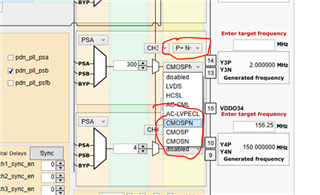

CDCI6214配置:

CDCE6214配置:

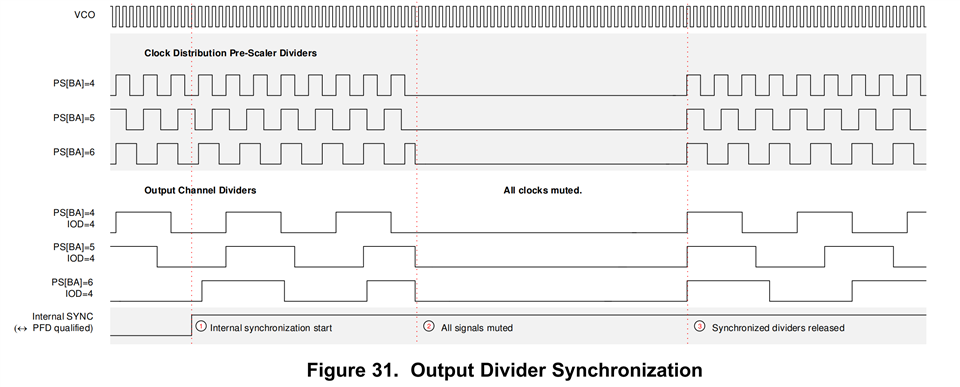

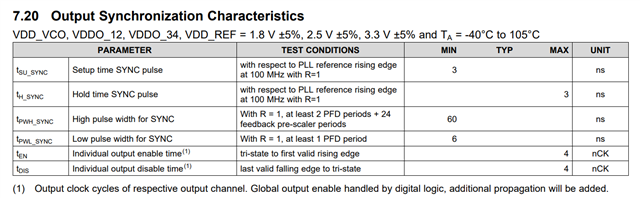

还有一个问题:CDCI6214和 CDCE6214都具有外部同步功能。 它可以使用 ch{x}_sync_DELAY 来实现最多32个周期的固定延迟。

周期频率是多少? 频率是多少?

2.如果我将同步时间设置为10个周期。 这意味着 SYNC 引脚上升沿到输出第一个边沿之间的延迟是10个周期吗?

3.如何在 CDCE6214配置页面中进行设置。 我可以在 CDCI6214配置页面中找到 SYNC 功能和延迟。 不在 CDCE6214中。

此致、

舒