您好!

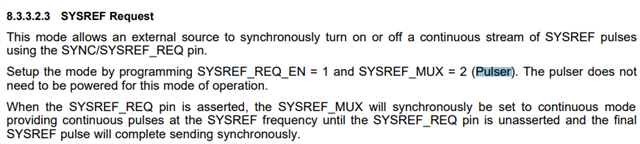

您能否对我用于从多个 LMK04832生成频率对齐和相位对齐时钟和 SYSREF 输出的预期实现进行彻底检查? 根据一些研究、我认为这应该会导致至少发生频率对齐的情况、但不确定相位对齐的准确度:

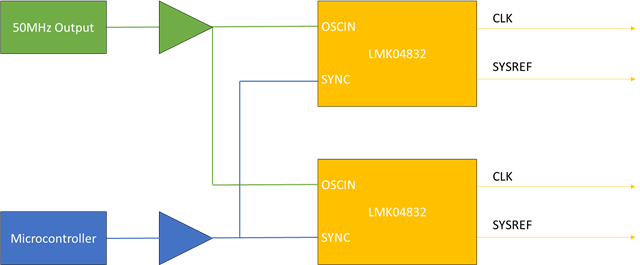

- 所有 LMK04832均使用外部环路滤波器在 PLL2单环路模式下运行

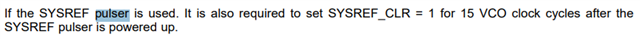

- 所有 LMK04832都在级联0延迟模式下工作、并且反馈多路复用器设置为 VCO 生成的内部 SYSREF

- 所有 LMK04832都接收到 OSCIN 的相位匹配50MHz 时钟输入、该 OSCIN 为 PLL2提供信号

- 所有 LMK04832都会接收到相位匹配的同步输入信号、该信号会触发多个 SYSREF 脉冲

在0延迟模式下、LMK04832之间从输入时钟到输出时钟的相位关系是否确定? 两个 LMK04832的输出是完全相位对齐还是存在一定容差?

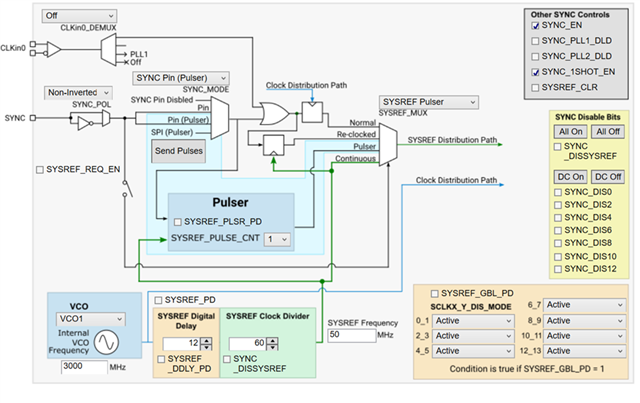

TIC 的一些方框图和图像以直观的形式呈现:

谢谢。

马修