请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:LMX2594 大家好、

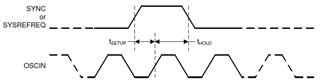

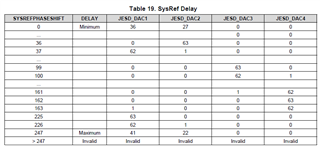

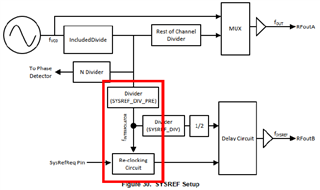

1.我的客户计划将时钟从 SysRefReq 引脚输出到 RFoutB。 在下图的 SYSREF 设置中、Re 时钟电路中的抖动是多少?

2.我的客户认为 Divider 的时钟将被时钟恢复,比上述频率落后多少次?

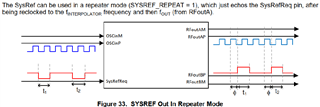

3.我的客户计划在 LMX2594的中继器模式下配置 SYSREF 输出。哪个信号应该与输入到 SysRefReq、OSCin?RFoutA 的信号同步?

4.关于 RFoutA 上的延迟 Φ、该延迟 Φ 是否始终相同? 或者延迟 Φ 是否有抖动?

此致、

山本俊介