您好!

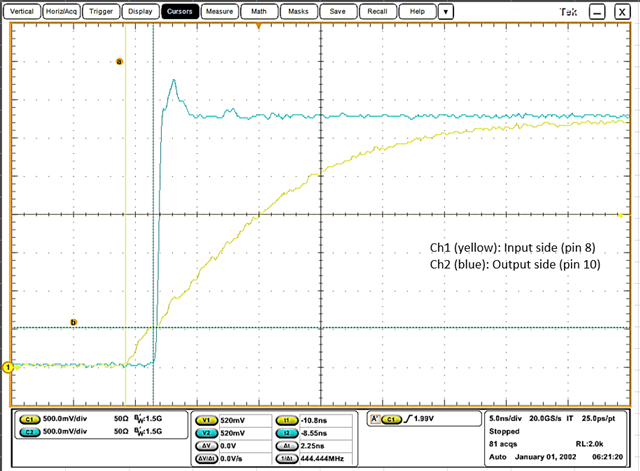

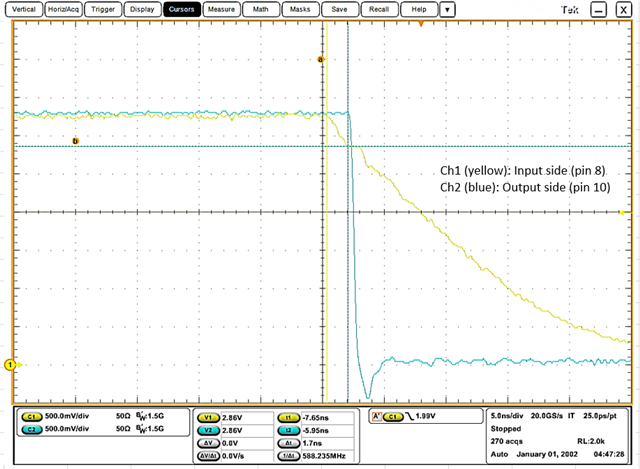

LVCMOS_CLK 引脚的 VIL 和 VIH 似乎不满足特性。 在不考虑 TPD = 1ns 至2.2ns 的传输延迟的情况下、所有4个通道的输出似乎在约0.45V 和约2.9V 时发生变化。

我们已使用官方的 TI 样片和商业购买的产品对此进行了验证、结果是相似的、似乎没有批次依赖性。

有可能得到任何意见吗?

谢谢。

科诺

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Conor、

我想我明白你在说什么。 规格 VIH 和 VOL 不以输入开关点为基准、而是以可接受的输入低电压电平和高电压电平为基准。 因此您的波形实际上处于规格范围内。 您的 VIL (输入低电压)为~0V、大于-0.3且小于1.3。 您的 VIH (输入高电压)是~3.3V,大于2,并且很可能大于 VDD + 0.3。

您是否遇到占空比问题? 如果您有任何其他问题、请告诉我。

此致、

将会

您好、 Will、

规格 VIH 和 VOL 不是参考输入的开关点,仅参考可接受的输入低电压和高电压电平。 [/报价]我根据数据表中的说明对其进行了以下解释。

当 Vin=-0.3~1.3V 时、Vout=Low 可保证为① μ A

②当 Vin=2.0~3.6V 时、Vout=高电平是可以保证的

③开关阈值介于1.3V 和2.0V 之间在您的回答中、似乎并不能保证输出为低电平、即使当 Vin =-0.3至1.3V 时也是如此。 有任何有关开关阈值的信息吗?

谢谢。

科诺

您好 Conor:

这似乎与我一直在 E2E 中处理的一个非常类似的问题相关(这是 链接 、但由于它是内部链接、我不确定您是否能够访问它)。

无论采用哪种方法、即使这是 LVCMOS 缓冲器(接收 LVCMOS 信号并输出 LVCMOS 信号)、输入驱动器也不会被设计为典型的 CMOS 驱动器。 相反、它充当差分驱动器。 我们按照数据表中所述标记了 V_IH 和 V_IL、因为您需要满足这些要求才能获得50%的占空比。 希望这对您有所帮助。

此致!

安德烈亚

尊敬的 Andrea:

抱歉、我不完全理解。

我的理解如下:

使用 LVCMOS、当它高于 Vdd x 50%时、被判定为 H 电平、当它低于时、被判定为 L 电平。 具体而言、当 VDD = 3.3V 时、阈值为1.65V (VIL/VIH)。

数据表中 VIL/VIH 代表什么? 另外、我不能看到 E2E 链接、所以如果您不介意、您是否能够重新设置格式以便从外部查看它并将其发送给我?

谢谢。

科诺

Conor、

很遗憾、我无法重新格式化 E2E 链接、因为它是内部 E2E、不能与非 TI 人员共享。

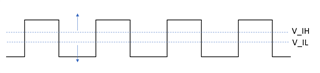

V_IH 和 V_IL 基本上可以确定您的信号需要摆动的限值、从而确保器件"看到"该输入。 可以将其视为信号需要摆动到这些值之外、以确保它大到足以被804B "看到"。

根据上图、信号需要摆动到 V_IH 和 V_IL 值之外、基本上朝箭头的方向。

不过、如果不需要50%的占空比、LMK00804B 并不会真正遵循此标准。 相反、需要实现大约200mV 的摆幅才能看到输出端的方波。

此致!

安德烈亚

尊敬的 Andrea:

感谢您的答复。

V_IH 和 V_IL 主要确定您的信号需要摆动的限制、从而确保器件"看到"该输入。 设想一下、信号需要摆动到这些值之外、以确保它大到足以被804B "看到"。

VIH 是当输入电压超过该值时被识别为高电平的电压、VIL 是当输入电压低于该值时被识别为低电平的电压。 我认为您的答案与常用的 VIH/VIL 定义相同。

正如我在第一篇文章中所述、我的问题是关于 VOUT 切换相对于 VIN 的时序。 在我第一篇文章的捕获中、当 VIN 大约为0.4V 时、Vout 从低电平切换到高电平、当 Vin 大约为2.9V 时、Vout 从高电平切换到低电平。 有关 VOUT 开关相对于 VIN 上升的时序和 VOUT 开关相对于 VIN 下降的规格、我应该参考数据表中的哪里?

Unknown 说:LMK00804B 在不需要50%占空比的情况下不会遵循此规则。 相反、需要实现大约200mV 的摆幅才能看到输出端的方波。

我对上述内容不了解、那么您能更详细地解释一下吗?

谢谢。

科诺

您好 Conor:

我的问题,正如我在第一篇文章中所述,是关于 VOUT 切换相对于 VIN 的时间。 在我第一篇文章的捕获中、当 VIN 大约为0.4V 时、Vout 从低电平切换到高电平、当 Vin 大约为2.9V 时、Vout 从高电平切换到低电平。 有关 VOUT 开关相对于 VIN 上升的时间和 VOUT 开关相对于 VIN 下降的时间规格、我应该参考数据表中的何处?

此行为是正确/预期的;不过、遗憾的是、数据表中未包含这些值。 我计划在下一次的数据表修订版中包含它们。 我们在实验室测试了开关阈值、并注意到了与您相同的行为。

我不明白上述内容,所以请您更详细地解释一下吗?

基本上、如果不满足 V_OH 和 V_IL、则无法保证信号具有50%的占空比。

此致!

安德烈亚