工具与软件:

您好、团队:

我有关于 CDCE913PW 的问题。

是否存在输出时钟频率不锁定的任何问题、例如频率保持移位?

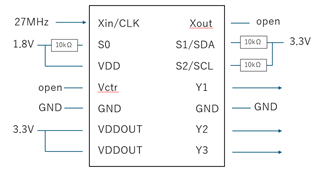

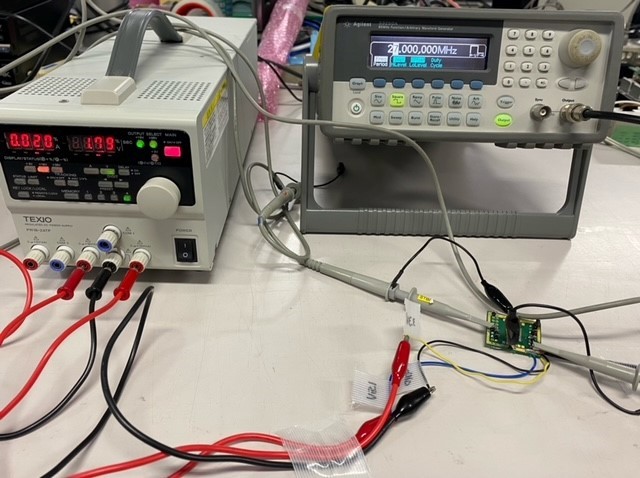

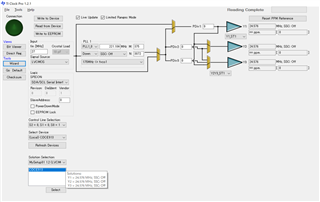

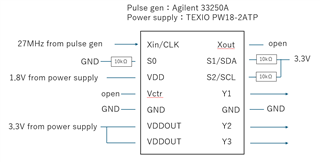

我们通过以下寄存器设置来使用此器件。

0x00:81 /0x01:09 /0x02:B4 /0x03:09 /0x04:03 /0x05:50 /0x06:40 /0x07:0 /0x08:0 /0x09:0

0x0A:0 /0x0B:0 /0x0C:0 /0x0D:0 /0x0E:0 /0x0F:0 /0x10:0 /0x11:0 /0x12:0 /0x13:0 /0x14:0D

0x15:01 /0x16:0 /0x17:0 /0x18:C0 /0x19:04 /0x1A:82 /0x1B:07 /0x1C:C0 /0x1D:04 /0x1E:82 /0x1F:07

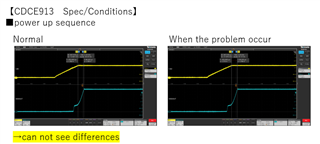

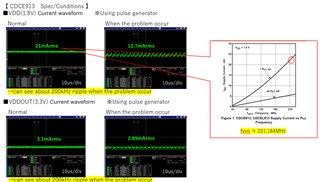

在极少数情况下、如果您关闭电源并再次打开、则输出频率会持续移动不需要的信号。(但 Y1Y2Y3输出端口处于同步状态。)

正如您在上述寄存器设置中所看到的、我们使用的 Y1Y2Y3输出端的频率与同一 div 相同。

首先、接通电源后、即使输出不稳定、时钟输出是否也是如此?

通常、一段时间后会输出一个稳定的时钟、但在极少数情况下(上述情况)、它会继续输出而不保持稳定。

我们猜测 PLL 有什么问题。

感谢您的支持