主题中讨论的其他器件:LMK04906、、、 LMK04208

工具与软件:

你好。

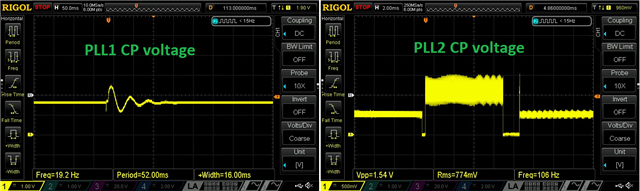

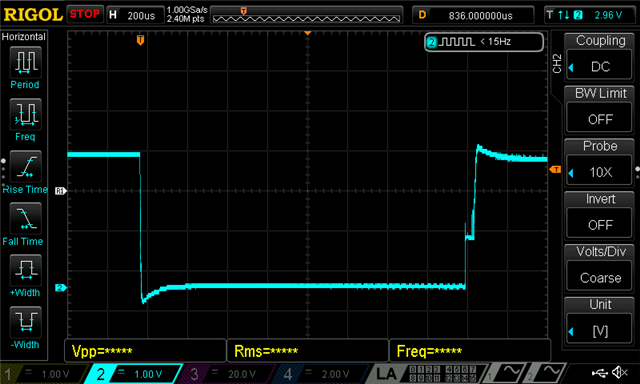

我具有正常工作的定制 PCB、LMK04906在双 PLL 模式下工作。 它与100MHz VCXO 配合使用。 我希望生成更高的频率、因此需要更大的内部 VCO 频率。 我找到了 LMK04808、它几乎与之相似、但具有更大的 VCO 频率。 我发现在 KVCO 的重要差异:16-21 vs 20-36。 我将其焊接到电路板上时考虑了引脚排列的所有差异(即大约5个电源/时钟输出引脚)。 它首次启动-输出正在发出信号、PLL1 DLD 显示始终锁定(在 LD_MUX 引脚上)。 但无法实现 PLL2 DLD。 我尝试与 PLL2预 N 分频器和 N 分频器值结合使用、并尝试更改 PLL2环路滤波器的外部部分(C1、C2、R2)。 使用 PLLatinum Sim 中建议的值、对于带宽~200kHz、C1=0、12n、C2=5、4n、R2=0、47k、 将 C2更改为其他值10n、2,7n 和 doug Bailey 在此论坛上创建的线程中的值(环路带宽1、5MHz)、我也尝试了评估板中的值、但 PLL2仍无法锁定。 我还使用 LD_MUX 引脚来测量频率、PLL2R/2上的频率正确(50MHz)、但在 PLL2N/2上仍然不正确(~58MHz 或~48M、取决于 Pre-N_Divider 和 N Divider 值)。 DAC 锁定/低电平/高电平为低电平。 在 LMK04906中、一切都正常工作、我几乎可以肯定、原因只是 LMK04906和 LMK04808的一些内部差异。 PLL2极性为负值、3、2nA、基准和相位检测器频率为100MHz。 我还可以查看或尝试哪些内容?

此致。