Other Parts Discussed in Thread: CDCE706, CDCE6214

主题中讨论的其他器件: CDCE6214

工具与软件:

您好、E2E 专家、

你好。

2024年6月25日

我正在设计一款接收模拟位的通用位同步器

数据流(通常被噪声污染)并使用输出数字数据

可以用来对数字化数据进行采样的时钟。

该设计需要一个时钟、其要求如下:

1.频率范围: 100 MHz 到320 MHz

2、频率分辨率:优于50 ppm

3、频率跟踪范围:+/- 10%

a:初始编程频率应跟踪中的变化

无任何干扰或相位的模拟输入数据速率

不连续点。

B.频率变化的速率将小于

1%/毫秒。

我们正在考虑将 TI CDCE706与中的 AD9850 DDS 配合使用

Analog Devices。 DDS 具有非常高的分辨率、可以提供高分辨率

可以改变的质量时钟、例如、从6 MHz 到16 MHz。

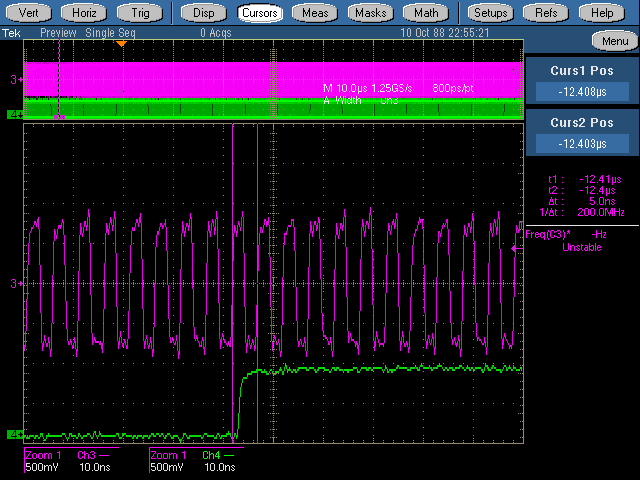

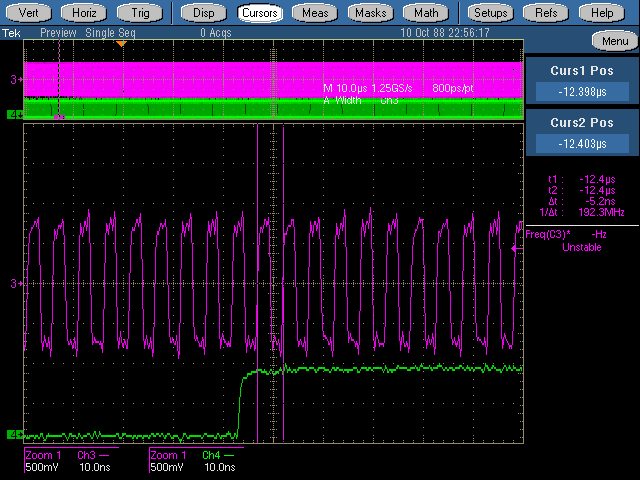

将通过连接 CDCE706的时钟来执行频率跟踪

DDS 输出的输入(注意 AD9850可以输出数字时钟)。

这将导致 VCO 平滑跟踪 DDS 上的小变化

调整。

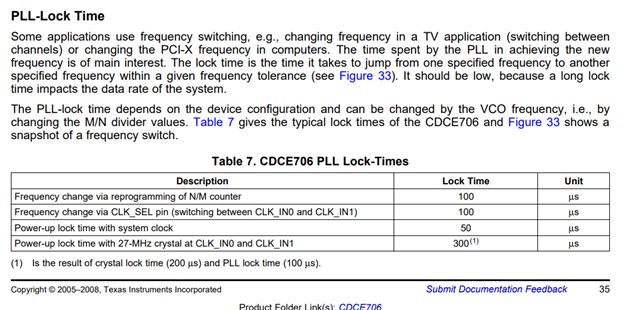

CDCE706数据表指出正常速度 VCO 范围为80

频率更改为200 MHz、并且高速 VCO 范围为180 MHz 至300

MHz。 不过、第7页的注释3指出 VCO 可以降低

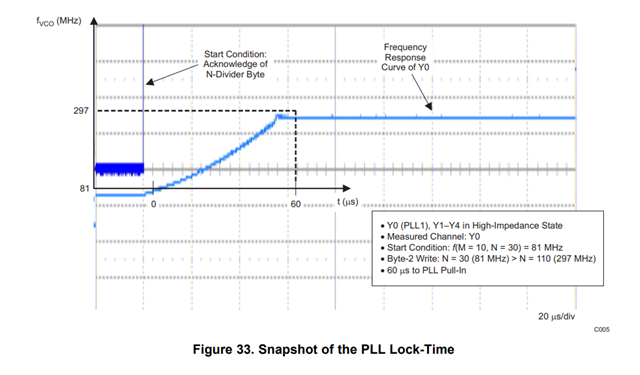

伴随相位噪声的降级。 第33页的显示了

正常速度 VCO 可以达到小于60 MHz 的范围

240 MHz 的电压范围、而高速 VCO 的电压范围实际上可以很宽

小于100 MHz 至大于320 MHz。 范围是否合适

有保证? 相位噪声的退化对我们没有意义

Application"。

请告诉我上述解决方案是否可行或有问题。

此致、

CSC