Other Parts Discussed in Thread: TPL5010

请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:TPL5010 工具与软件:

尊敬的 Expert:

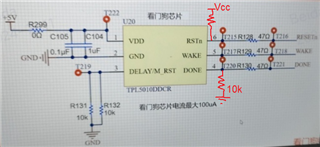

TPL5010的原理图如下所示、RSTN 为上拉、DONE 始终为狗提供喂食。

唤醒脉冲有时从20ms 减少到2ms 或8ms。 我怀疑此问题是由 VDD 的不稳定性引起的 、明天就会捕获波形。

您能提供一些其他建议以找到问题吗?