Other Parts Discussed in Thread: LMX2492

请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:LMX2492-Q1 Thread 中讨论的其他器件:LMX2492

工具与软件:

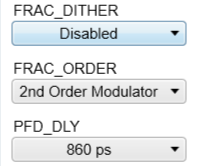

我还将 LMX2492用于 FMCW 雷达、发现使用线性调频脉冲功能产生的不良杂散。

与之前的设计人员一样、我也看到~11dBc 的杂散会产生 haystack 效果:

在外线之前、我必须检查时钟和电源、将其作为杂散的潜在来源、但现在我已在另一个线程中看到了该问题、我确信这主要是线性调频脉冲函数行为。

我使用非常纯净、低相位噪声的100MHz 参考、并且具有非常纯净且<-80dB 的电源噪声。

是否可以对设置进行配置、以更大限度地减小使用线性调频脉冲功能或一组建议的线性调频脉冲宽度/持续时间/频率范围时产生的分数 N 杂散、从而实现最佳性能?

此致、

Matthew