工具与软件:

II 想知道您是否有关于使用 LMK06318B (或更适合的其他部件)生成与 PPS 信号同步的156.25 MHz 信号的建议。 我提供了 PPS 信号的输入、以及与 PPS 同步且高达62.5 MHz 的可配置高频信号。 高频信号具有 周期必须为偶数纳秒(16ns 或更大)的限制。

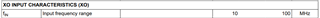

一种选择是使用可配置的高频信号作为 XO 输入、并将其乘以高达156.25 MHz。 例如、将其设置为31.25MHz、并将其乘以5。这仅使用 APLL。

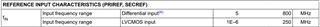

另一种选择(也可能更常见于此芯片)是使用 PPS 作为 DPLL 的基准输入、使用同步高频信号作为 XO、并使用 APLL1生成156.25MHz 信号。 我认为还可以使用零延迟模式生成 PPS 输出信号。

对这两种方法的相对优点有何意见? 156.25 MHz 信号与 PPS 同步的程度是重要的标准。