工具与软件:

您好!

A. 5G

B.4.4G

C.3.6G.

D.2.8G

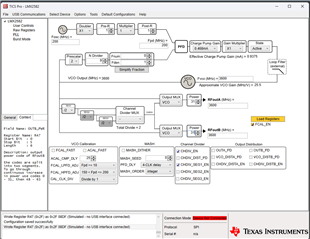

我能够对 LMX 编程以生成上述必需的时钟、还能够接收 PLL 锁定;但是、我 在配置 LMX 以生成3.6GHz 时钟时、无法实现 PLL 锁定(因此无法生成输出)。 我试着和他一起玩 TICS Pro GUI 看看是否任何组合都可以给我输出、但遗憾的是、无法成功。

我并不真正理解原因、因为即使在生成时、我也能够成功获得一个时钟 3.5GHz 进行采样。 我已经附加了十六进制寄存器转储、该转储在导出时 TICS Pro GUI 本身会提供。 我尝试了低功耗和最大功耗两种配置。

因为我正在处理可变采样率应用、所以我需要切换采样时钟以满足所需的规格、所以尽早提出任何解决方案/建议都将大有帮助。

e2e.ti.com/.../HexRegisterValues_5F00_3p6_5F00_maxpwr.txte2e.ti.com/.../HexRegisterValues_5F00_3p6_5F00_lowpwr.txt