Other Parts Discussed in Thread: LMK04821

工具与软件:

我已经在尝试计算 LMK04821器件的 SYSREF 和 DEVCLK 输出之间的延迟、但我根据数据表中的公式进行的计算似乎与我在电路板上测量的值不匹配。

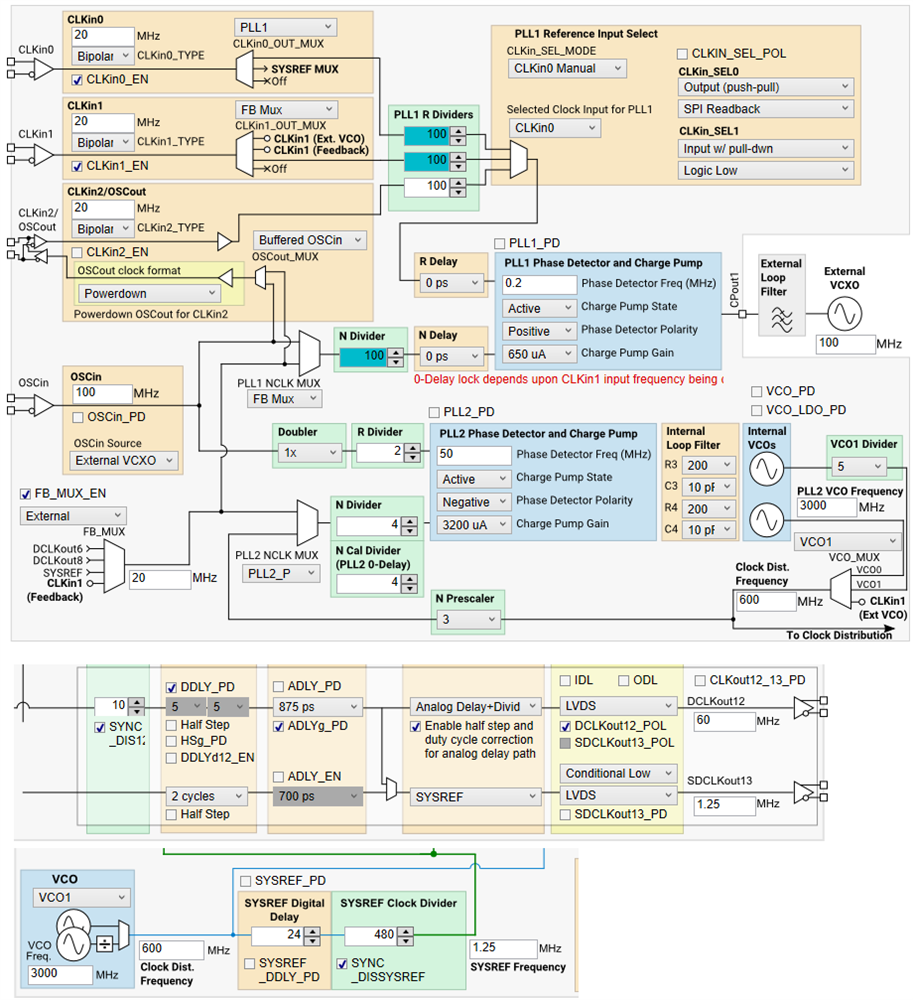

我已经附上了 TICS Pro 的 TCS 文件、供我们设置使用。

我们具有 LMK 的这些设置。 使用嵌套零延迟模式、通过用于 PLL1的100MHz VCXO 和带有/5预分频器的内部 VCO1来获得600MHz PLL2 VCO 频率。 外部反馈来自 DCLKOUT6、反馈到 CLKIN1中。 这似乎按预期工作(输入到输出延迟~0ns)、并且两个 PLL 均完全锁定。

我们使用外部 SYNC 引脚同步所有输出分频器、然后在完全锁定后、再次使用 SYNC 引脚在1.25MHz 上发送一组(四个) SYSREF 脉冲。

我使用一对差分探头测得 DEVCLK 上升沿和 SYSREF 信号上升沿之间的延迟为-4.1ns。 也就是说、SYSREF 在 DEVCLK 边沿之前上升4.1ns。

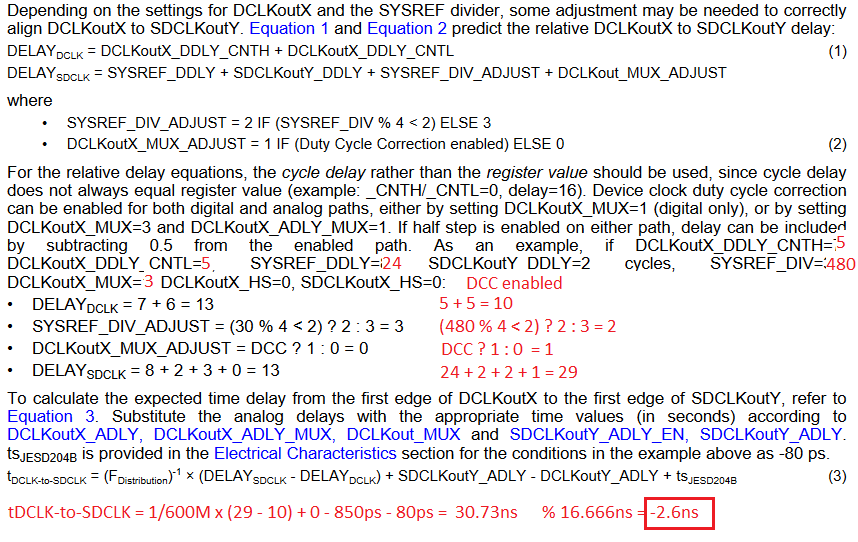

根据数据表9.3.4节 SYSREF 与器件时钟对齐、使用上述各种寄存器设置、我可以计算出"Tdclk-to-sdclk"延迟应为45.73ns。 如果我们从该值中减去3个 DEVCLK 周期、公式中建议的延迟应为-2.6ns。 使用以下信息:

请注意、DCC 已启用、因为在某些配置中、我们使用120MHz (/5)而非60MHz (/10)、并且两种情况下都需要一致的延迟。

您能不能就我的计算出的问题提供一点见解?