Other Parts Discussed in Thread: LMK05318B-Q1

工具与软件:

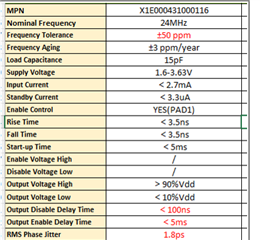

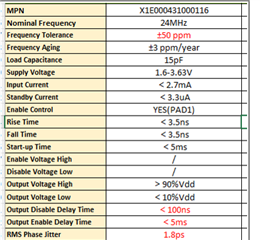

专家、您好、我想请问以下外部有源晶体振荡器参数是否符合 LMK05318B-Q1的设备要求? 非常感谢。

此致

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Other Parts Discussed in Thread: LMK05318B-Q1

工具与软件:

专家、您好、我想请问以下外部有源晶体振荡器参数是否符合 LMK05318B-Q1的设备要求? 非常感谢。

此致

尊敬的 Libin:

DPLL 有助于锁定到 从1PPS 到800 MHz 的任何频率的输入基准、从而为系统提供长期稳定性、因为它具有保持模式、可保持输出保持正确位置以防输入丢失并在输入恢复后重新锁定。

在自由运行模式下(仅使用 XO 基准时的 APLL)、如果 XO 丢失、输出将调优到不正确的频率。

锁定到1PPS 需要 DPLL、因为它需要0.01Hz 至 0.1Hz 等小环路带宽、并且如果使用晶体、ppm 太大而 无法实现小环路带宽的锁相。

-Riley