工具与软件:

大家好!

在我们的应用中、我们需要针对相对 数据动态地控制时钟的相位。

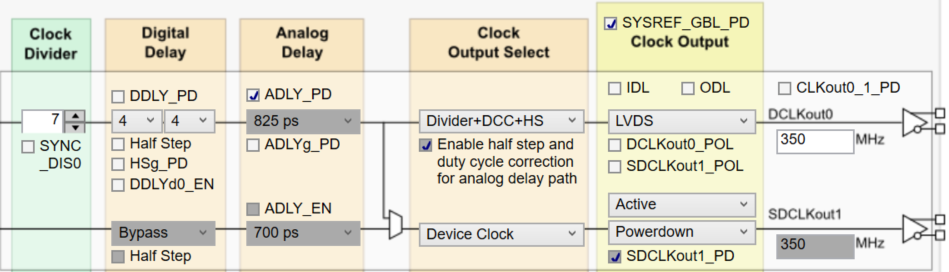

对于此应用、我们将尝试使用 LMK04828 (使用相对的演示板 LMK04828EVM)、并遵循零延迟模式下350MHz 输入和输出时钟的数据表配置。

输出与输入同步。

我们 可以正确地应用模拟延迟、但问题在于数字延迟:

我们无法通过数字延迟来"稳定"地控制时钟的提前或延迟。

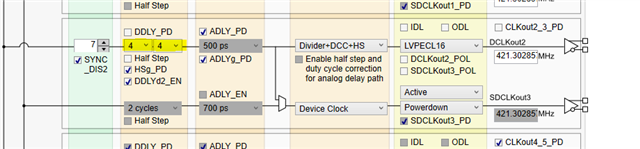

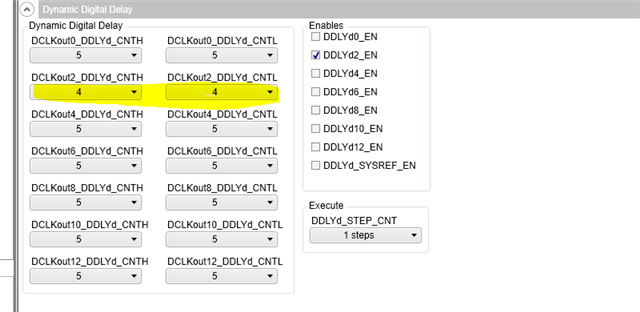

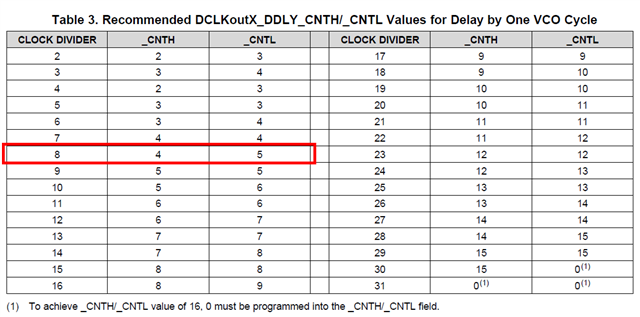

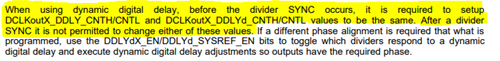

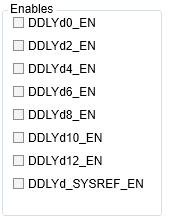

时钟使用内部分频器7、因此按照"9.3.3.2动态数字延迟"一节中所述的 步骤操作、并为 DCLKoutX_DDLY_CNTH/_CNTL 设置一个单步延迟值:

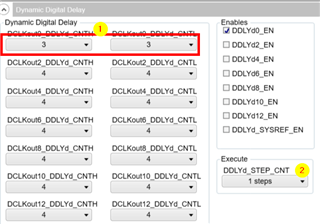

向前: _CNTH = 4. 并且_CNTL = 4.

反向运行:_CNTL = 3. 并且_CNTL = 3.

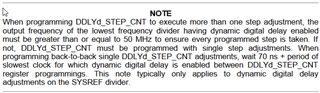

在应用 DDLYd_STEP_CNT = 1后、 希望它能为时钟相位或前向或后向提供每次1个简单步长的时间(取决于先前的 DDLY_CNT)。

幸运的是、使用自动测试将时钟向前移动3步、向后移动3步、我们注意到、有时有一个使步进加倍的意外移动、导致总共提前(或 延迟)步进4步、而不是预期的3步。

对于我们来说、必须具有稳定且可预测的相位延迟。

配置是否有问题?

我们还可以尝试其他什么、还是这是一种预期行为?

提前感谢。