请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:LMX1214 工具与软件:

您好!

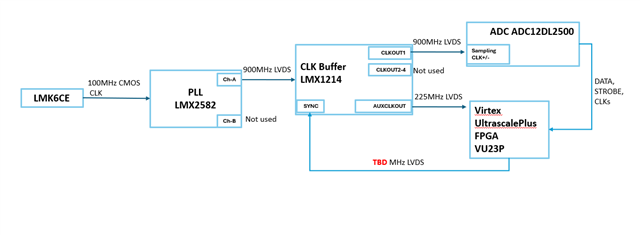

我们有如下所示的实现方案、要求 ADC 采样时钟和 FPGA 都有一个通用时钟源。

由于 FPGA 无法获取900MHz 输入(来自 PLL 的 CH-B 或 ClkBuffer 的 CLKOUTS2-4)、我们计划使用来自时钟缓冲器的 AUXCLKOUT 引脚的225MHz LVDS。

根据我对同步 CLKOUT1和 AUXCLKOUT 输出的理解、SYNC 引脚是必需的。

1)正确吗?

2)如果需要、我们将考虑发送 SYNC 输入以及时钟缓冲器配置设置、这些设置将在时钟缓冲器开头通过 SPI 进行编程。

您可以确认一个同步触发足够从 FPGA 在缓冲器启动时连同其他 SPI 配置设置一起发送吗?

3) 3)对时钟缓冲器的同步 LVDS 触发输入是否有任何频率要求?

谢谢