工具与软件:

尊敬的团队:

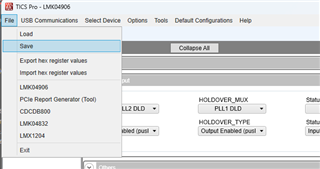

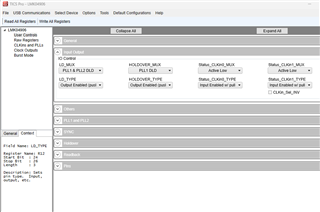

现在我们用 LMK04906完成设计并配置器件使用以下寄存器值。

R0 (初始化) 0x80160200

R0 0x00140300

R1 0x00140301

R2 0x00140302

R3 0x00143C03

R4 0x00140784

R5 0x80140C85

R6 0x01140006

R7 0x08110007

R8 0x04080008

R9 0x55555549

R10 0x9102412A

R11 0x0401100B

R12 0x1B0C006C

R13 0x3B02848D

R14 0x0240000E

R15 0x800800F

R16 0xC1550410

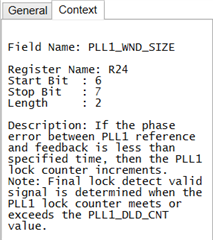

R24 0x000000D8

R25 0x02C9C419

R26 0x8FA8001A

R27 0x1900005B

R28 0x0020011C

R29 0x0180031D

R30 0x0200031E

R31 0x001F001F

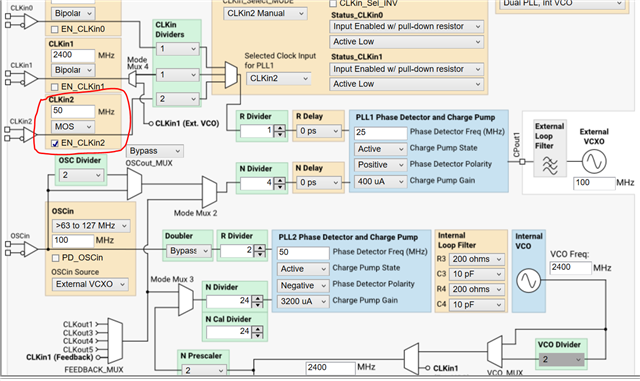

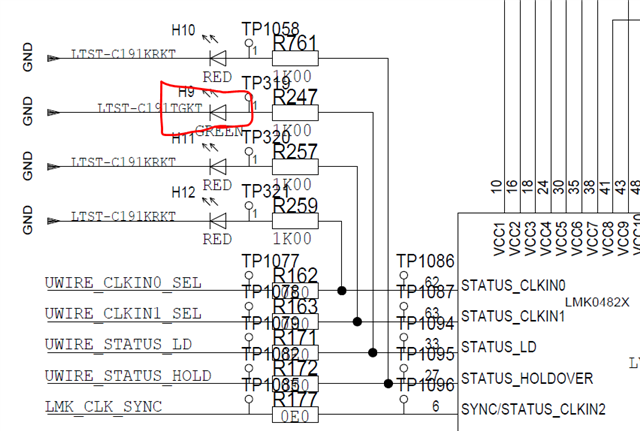

我认为对于 PLL1和 PLL2已经在上述配置后被锁定。 根据我下面的原理图、H9必须开启。 而现在、H9仍处于关闭状态。

您可以帮助我们仔细检查您的评估板吗?

我们以 CLKin2作为参考、采用的是来自 Keysight 信号发生器(输出功率为5dBm 的 N5182B)的50MHz 正弦波。

外部 VCXO 为 VX-501-0208-100M0 。