Other Parts Discussed in Thread: LMK1D2106, LMK1D2104

主题中讨论的其他器件: LMK1D2104

工具与软件:

您好!

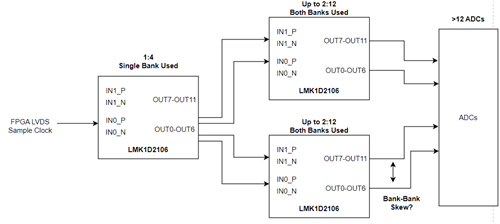

我正在围绕 LMK1D2106器件进行设计、适用于高速 ADC 应用、其中我们将 FPGA LVDS 样本时钟扇出到超过12个 ADC (无法指定实际计数)。 我们选择了使用这一级联芯片、以便以最小的时序偏差和几乎相同的传播延迟将相同的信号扇出到我们的所有 ADC。

我们计划在上游 LMK1D2106器件的一个组上使用多个输出、以驱动下游器件上的两个双输入、从而在我们的设计中更大限度地提高每个器件的扇出/更大限度地减少器件数量。

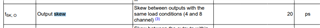

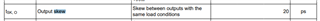

我们针对 ADC 同步有一些严格的时序要求、虽然定义了同一组内的输出偏斜(tsk、o)和器件间偏斜(tsk、pp)、但似乎没有针对同一部件内的组间偏斜的数据表规格。 最坏情况下、我们假设这不比器件间偏移差、但我们希望获得更具体的数字。 已了解总计时偏斜将是一个层叠、其中还包括来自第一级 IC 之间的 tsk、o 和 tsk、pp 的偏斜。

如果两个输入都由"相同"(即同相)信号驱动、您能否确认 LMK1D2106的组间输出偏差是多少?

pic、目标配置如下。

(simear——LMK1D2104可以用于第一级、但同样的 IC 更具 BOM 效率、并且在将来可以灵活地增加扇出比)