工具与软件:

您好!

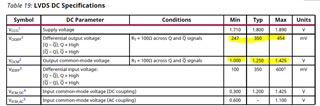

我们需要将 FPGA LVDS 输出连接到 SYNC 引脚。 基于以下 FPGA LVDS 输出规格、共模和差分似乎都超出规格。

适用于1V 至1.425V 的 FPGA 输出。 SYNC 引脚的 VCM 从1.2V 开始。

同样、FPGA 的 Vodiff 为247至454mV。 但对于 CB、它的起始值为0.6/0.8V

您可以建议 如何将这些信号耦合到 FPGA 上吗?

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

工具与软件:

您好!

我们需要将 FPGA LVDS 输出连接到 SYNC 引脚。 基于以下 FPGA LVDS 输出规格、共模和差分似乎都超出规格。

适用于1V 至1.425V 的 FPGA 输出。 SYNC 引脚的 VCM 从1.2V 开始。

同样、FPGA 的 Vodiff 为247至454mV。 但对于 CB、它的起始值为0.6/0.8V

您可以建议 如何将这些信号耦合到 FPGA 上吗?

LMX1214 VCM 是差分输入处于平衡状态的电压(没有电流从 P 流向 N)。 您的 FPGA LVDS 的 VCM 大约为1.2125V、可满足 VCM 要求。 信号幅度规格指定为2 *|Vp - VM|(我们不在任何地方提及)、这意味着|Vp - VM|= 425mV 的 LVDS 足以实现直流或交流耦合。

通常情况下、FPGA LVDS 输出中的 Vcm/振幅范围是可编程的-这些规格是代表一系列可能的可编程值、还是代表标称 LVDS 输出的实际完整范围可能的 Vcm/振幅? 如果是前者、则没有问题。 如果是后者、您可能应该对 LVDS 进行交流耦合。

LMX1214数据表极大地破坏了 SYNC 输入的建议运行条件、因此我将尝试解释运行原理:

我会尽力将这些说明插入 LMX1214数据表中的某个位置。阅读没有说明的假定约定、值基本上是从空气中拉出、以及不明显的 LVDS 兼容性是很令人沮丧的。

尊敬的 Derek:

感谢您花时间提供见解。

FPGA 数据表中指定的 LVDS 限制是完整范围且不可编程。

接下来、您能否确认我下面对您解释的总结是否 正确?

1.尽管 FPGA LVDS 输出将为 1V 到1.425V (没有调优选项)、但由于 Clkbuffer 可以读取 1V-2V、因此可以实现共模电压兼容性。

2.即使 FPGA LVDS 输出摆幅将为247-454mV、但由于其输入差分电压能力为200mV 至~600mV、因此时钟缓冲器可以读取此输出。 因此、还实现了差模电压兼容性。

3.根据第一点及第二点、我们可以采用直流耦合端接、如图7-4所示

谢谢

知道这是不可编程的、我们确实有一个角落可能有问题:假设共模电压为1V、Vodiff 为600mV。 在这种情况下、对于任何直流耦合、我们会在稳态条件下在其中一个输入端主动驱动0.7V。 这可能会影响同步输入放大器的压摆率、从而影响时序稳定性。

如果您的 FPGA 可以采用这一拐角、则应根据数据表中的图8-2对信号进行交流耦合。 我建议将内部偏置设置为"无"(就像直流耦合)、并使用外部电阻器来设置偏置。 虽然 数据表建议 SYNC_P 和 SYNC_N 之间的电势至少为150mV、但如前所述、在100mV 下工作也是如此。 当 R2 = R3 = 1kΩ 时、您将获得大约120mV 的电压、这大约会在 FPGA 输出仅为250mV 摆幅的最坏情况下拆分差异、以便在逻辑高电平和逻辑低电平条件下各自的引脚上都出现±125mV 的电压。 同样、对于高达450mV 的脉冲输入、SYNC_N 引脚将从稳态引脚下拉至不低于0.9V。

在该方案下、可能会出现瞬时情况、如果输入幅度为450mV、输入为逻辑高电平、并且交流耦合网络已经稳定、SYNC_P 从1.13V 开始- 450mV 输入脉冲可能会将 SYNC_P 电压暂时下拉至0.68V -因此我建议对 SYNC 输入进行脉冲来避免这种情况、 否则、请确保 在将 SYNC 输入恢复到逻辑低电平时未启用 LMX1214中的 SYNC 子系统、并让输入有足够的时间恢复到标称偏置。

另一方面、如果 FPGA 的 Vcm 和 Vodiff 呈线性相关、以至于在1V Vcm 时出现250mV 摆幅、而在1.425V Vcm 时出现450mV 摆幅、则 Vcm 和 Vodiff 之间具有连续的比例关系、直接直流耦合可以满足所有要求。 我怀疑 VCM/Vodiff 像这样线性相关,但我提到它只是为了以防万一,因为它会简化故事。

尊敬的 Derek:

谢谢

为延误道歉...

a)是、在运行的剩余时间内将 SYNC 保持在逻辑高电平应该仍然适用于交流耦合。 当发生系统级重新启动时、将会出现瞬时情况、其中 SYNC 信号从 FPGA 返回逻辑低电平、 引脚电压的绝对值降至0.8V 以下、在此期间应等待引脚电压恢复到交流耦合的默认偏置-您可以通过直接的 SPICE 仿真来估算这需要多长时间(假设 LMX1214内 SYNC_P 到 SYNC_N 的路径是100Ω 电阻器、这对于时序估算足够接近)、 并且、您应该能够 减小交流耦合电容器的尺寸、从而缩短等待持续时间(以及 SYNC_P/SYNC_N 引脚产生的脉冲宽度)。

B)您可以在板上保留交流和直流耦合选项、数据表中推荐的电路建议了一个外部无源网络、该网络应允许根据需要在交流和直流耦合选项之间切换。