Other Parts Discussed in Thread: LMK04828, LMK04821, LMK04826, LMK04828BEVM

主题中讨论的其他器件: LMK04821、 LMK04826、

工具与软件:

您好!

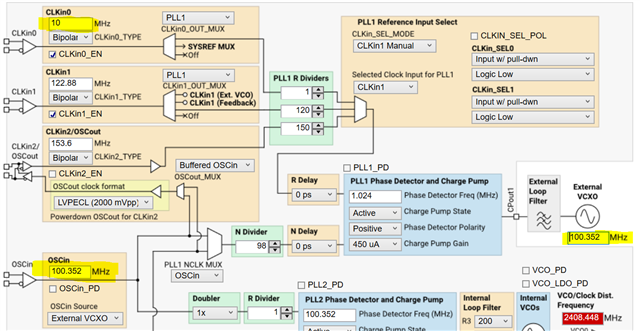

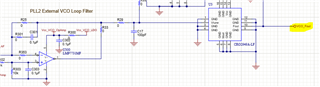

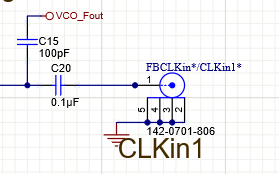

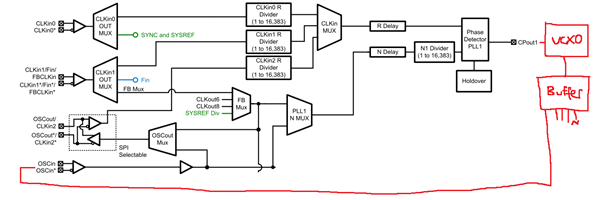

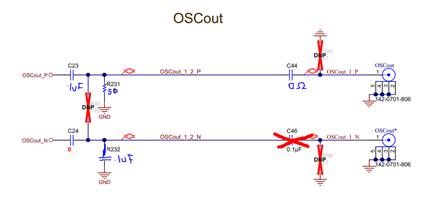

我们考虑 将 LMK04828 PLL 集成到我们的设计中、

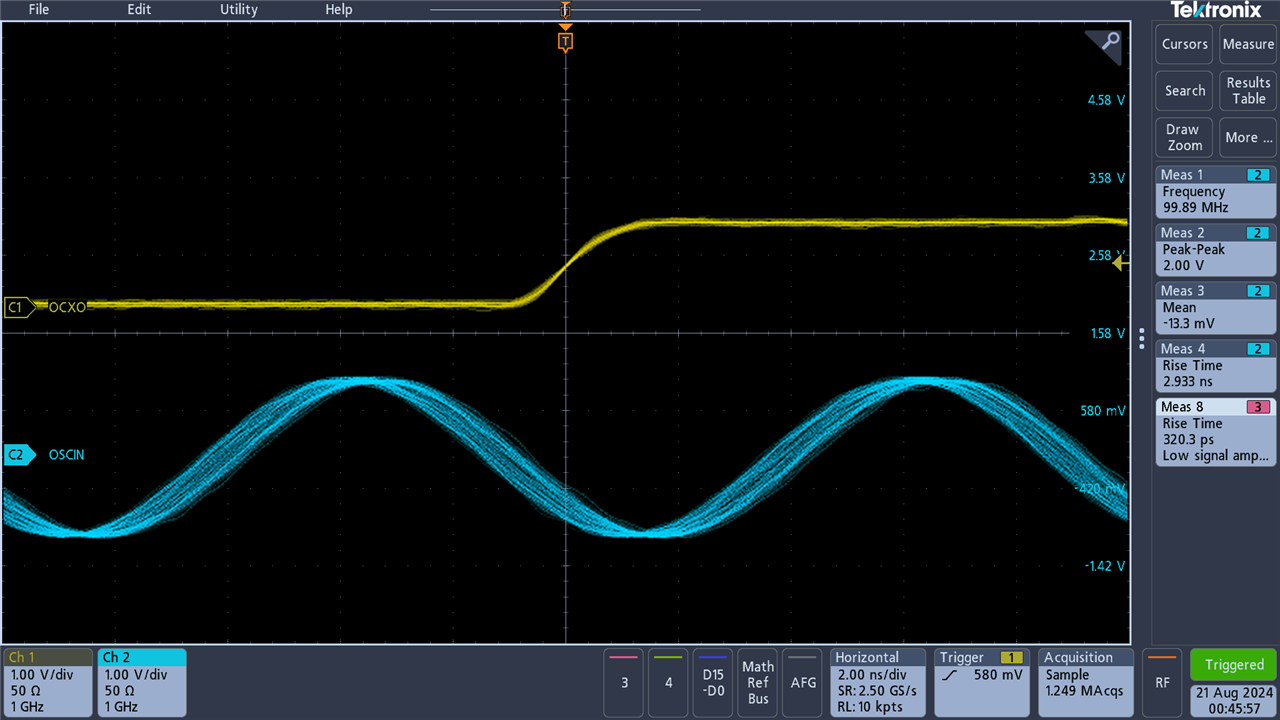

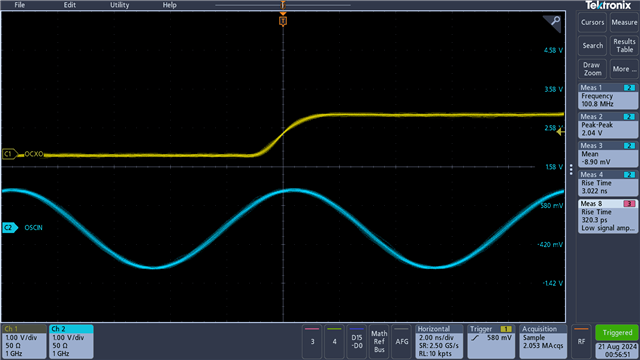

PLL 的目标是从三个10MHz 正弦波基准中选择一个基准并生成一个100MHz 输出。

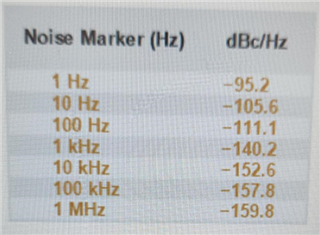

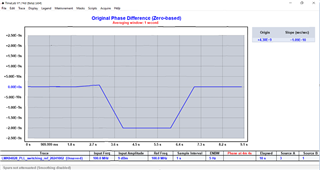

由于基准源非常纯净且相位噪声较低、因此我们希望保留信号的相位噪声。

问题:

1) 1) LMK04828是否使用100MHz 进行相位噪声测量?

2) 2)使用10MHz 正弦波作为 LMK04828的基准输入是否存在任何限制?

3)我们可以用 CVHD-950-100替换板载 VCXO 吗? 这与封装兼容。

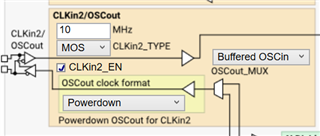

4) 4)我们可以将 OSCIN (VCXO 输出)用作 PLL 输出吗? 在这种情况下、我们仅使用 PLL1

5) 5) LMK0482x 系列包含多个 PLL。 根据上述要求、我们如何选择最佳 P/N?

6) 6) LMK04828的 TICS Pro GUI 支持.TCS 文件配置。 如何准备与此文件扩展名兼容的配置?

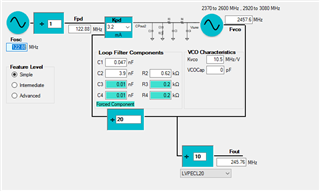

我们已经尝试 使用时钟设计工具和 PLLatinum Sim、但这两个配置文件都有不同的扩展名、GUI 不支持它们。

电子邮件:alse@gmv.com

提前感谢、

Alon Sechan