工具与软件:

我们希望 LMX1204生成的 CLKOUT 和 SYSREF 之间具有固定相位关系。 使用 LMX1204进行时钟和 sysref 同步时、相位不能固定。

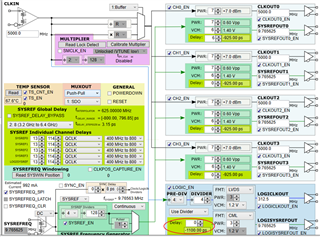

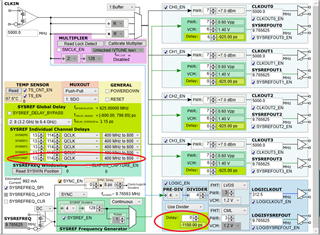

通过对 LMX1204的 CLKIN 进行分频生成四个 SYSREFOUT、一个 LOGICLKOUT 和一个 LOGISYSREFOUT、并通过 缓冲器功能生成四个与 CLKIN 频率相同的 CLKOUT。

在当前配置中、SYSREF 使用连续模式、SYSREFREQ 通过我们的控件具有单个脉冲 LVDS 电平输入。

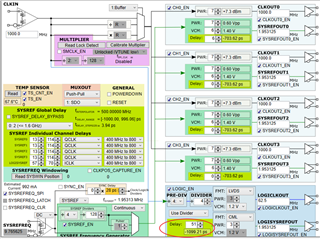

LMX1204生成四个 CLKOUT、四个 SYSREFOUT、一个 LOGICLKOUT 和一个 LOGISYSREFOUT 后、我们按如下方式修改配置:

1) 1) 将 SYSREFREQ_N 电平设置为1.4V、将 SYSREFREQ_P 电平设置为1.0V

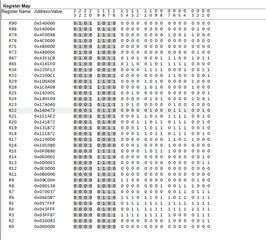

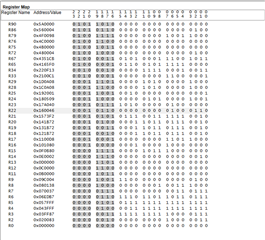

2) 2)修改 LMX1204寄存器:

0E、0100

09、E004

0F、0B84

3) 3) 将 SYSREFREQ_N 电平设置为1.0V、将 SYSREFREQ_P 电平设置为1.4V

但是、在此配置之后、无法保持 SYSREFOUT、LOGISYSREFOUT 和 CLKOUT 之间的固定相位关系。