Other Parts Discussed in Thread: LMX2572EVM

工具与软件:

您好!

我在 LMX2572EVM 上进行了一些测量、但结果很奇怪。

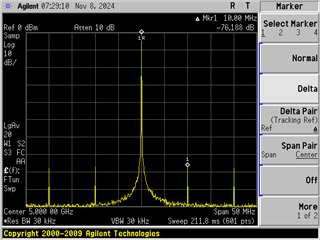

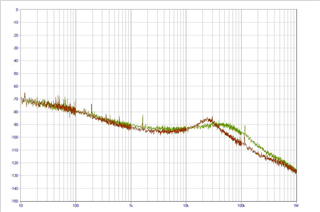

首先、关于输出相位噪声、我在输出频率设置为5000 MHz 的情况下进行了测量(默认硬件配置、使用参考 PRO 板的100 MHz)。

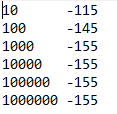

我得到了以下结果:

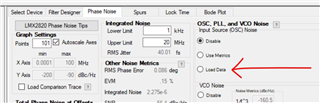

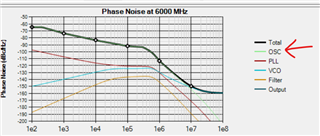

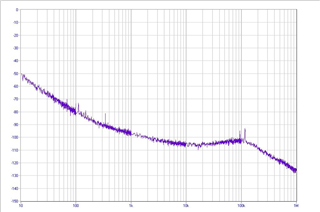

而仿真(使用 PLLatinum Sim 软件)给出了这种情况:

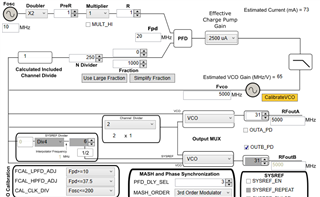

ICP = 2、50 mA 在仿真和评估配置中。

我们如何解释这种区别?

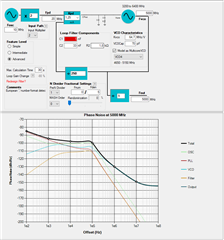

在另一种配置(启用参考倍频器的10 MHz 参考)中、对于设置为4960 MHz 的输出频率、仿真给出:

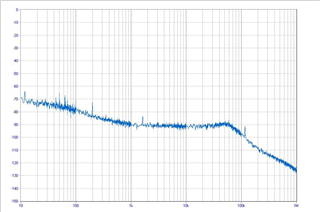

而评估板上的测量结果表明:

同样、两者之间存在很大的差异。 怎么解释?

在测试过程中、我还注意到、根据在 LMX2572EVM 基准输入处注入的外部10 MHz 基准信号电平、相位噪声响应不同:

3dBm 时基准电平的绿色曲线和+7dBm 时基准电平的棕色曲线。

如何解释此环路滤波器带宽变化?

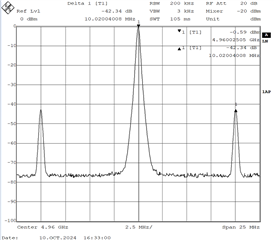

最后、在测量输出频谱时(始终处于启用10 MHz 外部基准和基准倍频器的4960 MHz 处)、我注意到- 10 MHz 杂散、抑制效果不佳:

实际上、抑制取决于 ICP 设置:从最大值(6、875 mA)时的42 dB 到最小值(0、625 mA)时的63 dB。

这是正常行为吗? 在将 ICP 电流设置为非最小值(以获得最低相位本底噪声)时、获得优于60dB 的抑制的最佳方法是什么?

禁用倍频器后、这些杂散会消失(或抑制优于80dB)、但相位噪声结果会降级...

提前感谢您的帮助。

Alain